# **THE FUTURE OF LOGIC** Gate-All-Around Is Here, Now What?

#### Bala Haran

Vice President, Integrated Materials Solutions Semiconductor Products Group

#### **2019 Panel Takeaways**

#### **EUV Is Here, Now What?**

- AI beginning to shape the technology roadmap

- New approaches needed to drive innovation

- Requires co-optimization from materials to systems

A new playbook for collaborative innovation

#### What's Changed Since 2019?

## GAA Is Here, Now What?

**Nick Yu** Google **Custom Silicon** Technologist

Qualcomm VP of Engineering

PR Chidambaram Kevin Fischer Intel VP, Interconnect and Memory Integration

**Dong-Won Kim Geoffrey Yeap TSMC** Samsung Fellow, Logic VP, Research & Technology Development Development

**Victor Moroz Synopsys** Fellow

**Paul Lindner EV Group** Executive **Technology Director**

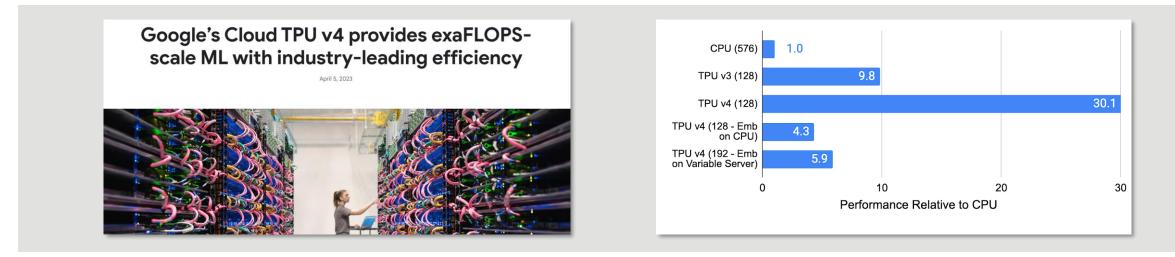

### Google's Cloud TPU v4

Google

#### Google's Cloud TPUv4 enabled:

- a nearly 10x leap forward in scaling ML system performance over TPU v3

- boosting energy efficiency ~2-3x compared to contemporary ML DSAs, and

- reducing CO2e as much as ~20x over these DSAs in typical on-premise data centers

TPU v4 provides exascale ML performance, with 4096 chips interconnected by an internally-developed industry-leading optical circuit switch (OCS).

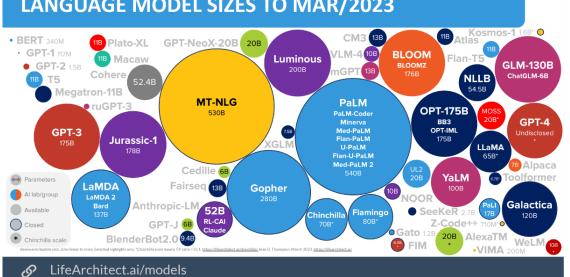

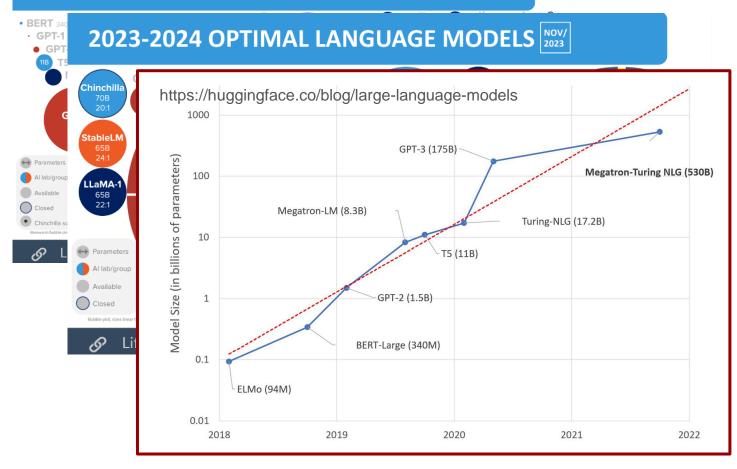

#### LANGUAGE MODEL SIZES TO MAR/2023

#### LANGUAGE MODEL SIZES TO MAR/2023

#### LANGUAGE MODEL SIZES TO MAR/2023

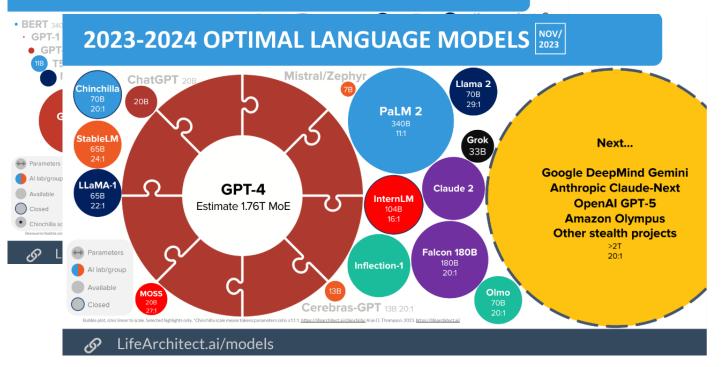

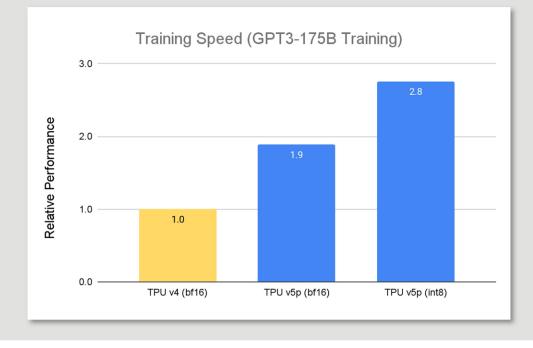

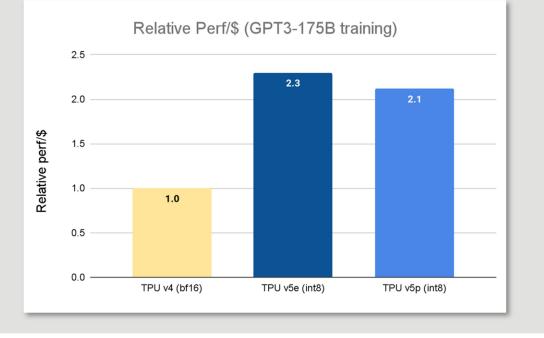

#### Google's Cloud TPU v5 [Announced 6th Dec 2023]

#### Will GAA/Nanosheet trajectory keep up with LLM's growth?

### Gen AI to Accelerate Innovations in Our Industry

#### **Key System Themes**

- GPUs vs DSAs

- Memory (more HBM, what's next)

- Chiplets (what's next)

- Interconnect (optical)

- Thermal

- Security

- Technology guardrails

#### **Digging Deeper**

- Die size scaling, intrinsic area scaling

- » Computation and Power density

- New memory overcome logic-to-memory bottleneck

- Perf/TCO(OpEx) vs Perf/CapEx

- » Thermal/Power

- Silent Data Corruption eliminate/early-detect soft defects?

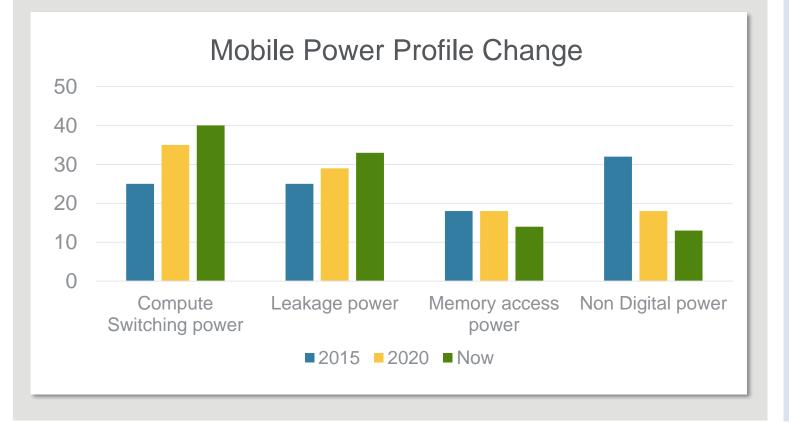

### Digital Switching and Leakage Power Will Limit Industry Qualcomm

- Product power reductions slowing for lack of true universal curve gain

- Multi-die/Chiplet mostly help with memory access power

- DTCO based power gains advertised hard to realize on product

- Vdd and leakage reduction essential

#### 2023 2019: "The Future of Logic. Gate All Around EUV is Here, Now What?"

- The State of Logic is STRONG (5nm mass production in 1H '20) N3/N4/N5 in mass production

- The Future of Logic is BRIGHT (3nm and 2nm in development)

2nm MP in 2025

- Adv. Logic Tech:

- 1) Mobile AI mobile

- 2) High Performance Computing AI data center scale computing

- 3) Automotive AI driving

- 4) IOT AI everywhere

- PPACt: traditional scaling → DTCO scaling → system scaling/integration

- Power supply scaling and low Vdd operation

- More energy-efficient and high-performance transistors

- Houston, we have a problem: Interconnect Resistances BSPDN

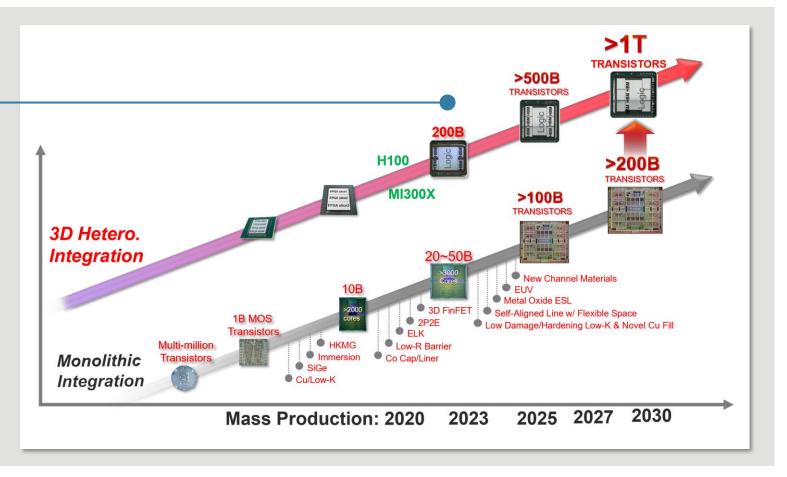

### System Scaling Innovation

Enabled by TSMC Adv Logic + 3DFabric™ (CoWoS, SolC, and InFO) Technologies

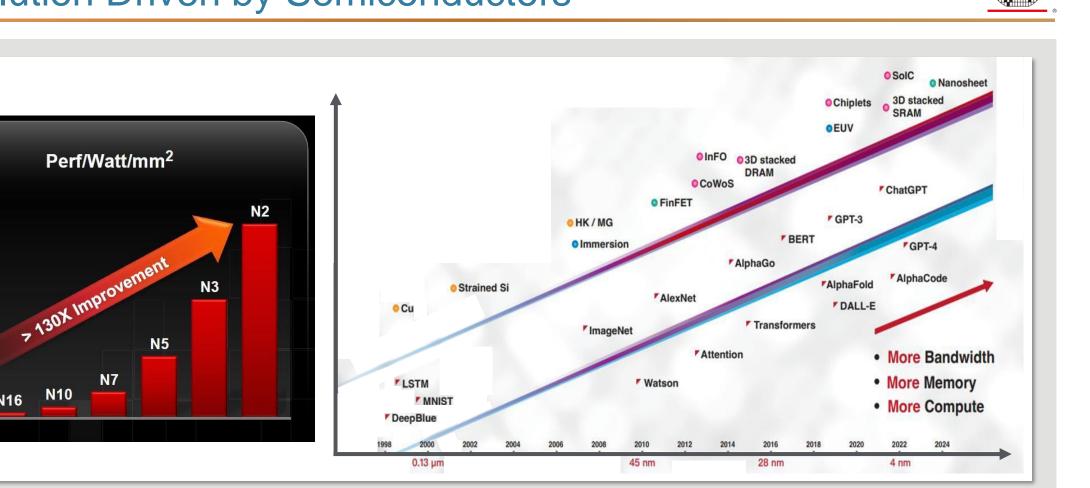

### Al Revolution Driven by Semiconductors

N7

N10

N16

N28

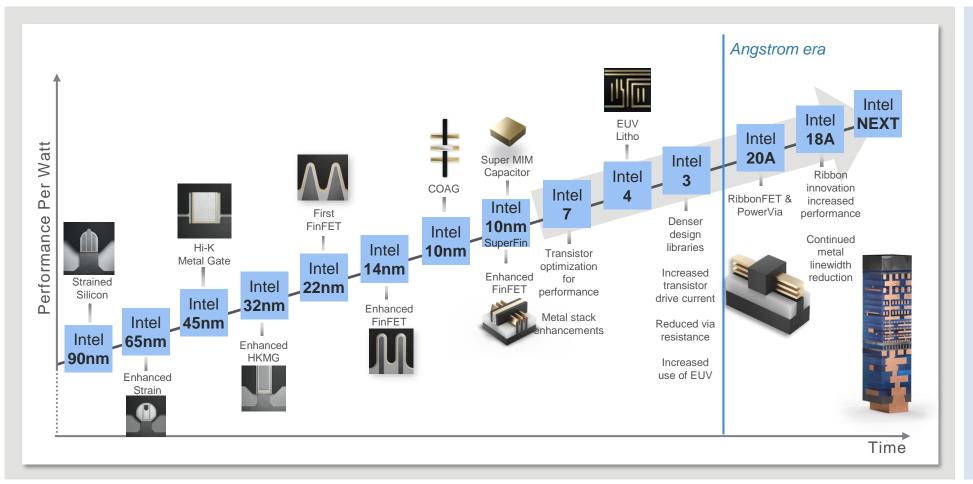

### Intel Roadmap: Next Step in 5 Nodes in 4 Years

#### PowerVia and RibbonFET on Intel 20A and Intel 18A

intel

- Improved perf. per watt

- Improved density

- Reduced node over node cost increases

- Improved design flexibility

Learn more at <u>www.Intel.com/ProcessInnovation</u>

### Frontside Power Delivery vs PowerVia

#### **Frontside Power Delivery**

Signal wires and power wires compete for the same resources at every metal layer

Requires aggressive scaling of metal layer pitches:

- High cost

- Higher voltage droop

- Higher RC delay

Intel Innovation 2023

#### **PowerVia Backside Power Delivery**

Signal wires and power wires are decoupled and optimized separately

#### Value Proposition:

- Better Performance

- Lower signal RC

- Reduces voltage droop

- Lower Cost

- More Design Flexibility

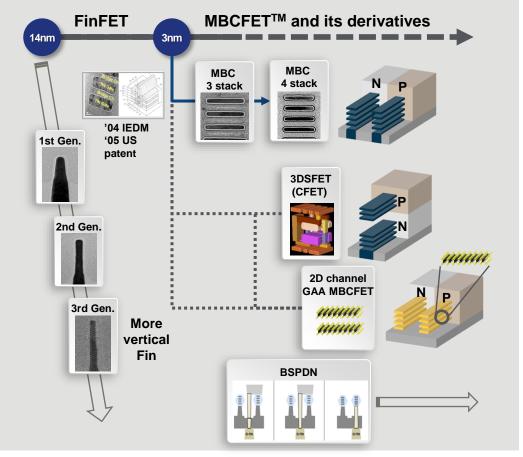

### MBCFET<sup>™</sup> Learning and Future

MBCFET (Multi-Bridge-Channel FET)

#### Key Messages

- Learnings from the 3nm MBCFET ramp

- » Metrology & Inspection

- » Limited spacing for metal gate

- » Co-optimization of devices with wide/narrow widths

- View of the roadmap for upcoming inflections

- » Extending the MBCFET era

- Additional nanosheets for enhanced drive current and cell scaling

- Introduction of CFET and/or BSPDN for STD cell scaling extension

- Implementation of 2D Materials in GAA MBCFET architecture

- » Implementation of backside power delivery

- Improved IR drop and area gain corresponding to frontside PDN

- Additional performance/power gain and increased design freedom with less congestion

- Increased the difficulty of DTCO and STCO to utilize BSPN

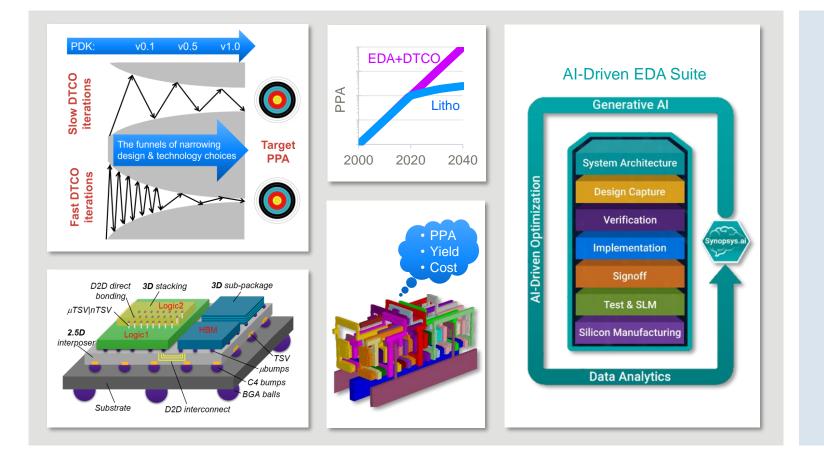

### EDA Role in Advanced CMOS Eco-System

### **SYNOPSYS**<sup>®</sup>

#### **Key Messages**

- Collaboration with Foundries & Fabless to Optimize EDA tools for

- » GAA & CFET (Si, SiGe, stress)

- » BS PDN (power, clock, signal)

- » Chiplets (hybrid bonding, I/O devices)

- » Library optimization (track height mix)

- Fast DTCO exploration to boost PPA for specific chip applications

» 3 days turn around time

- Collaborative and Generative AI

- » DSO.ai (Design Space Optimization)

- » Synopsys.ai Copilot (full EDA stack)

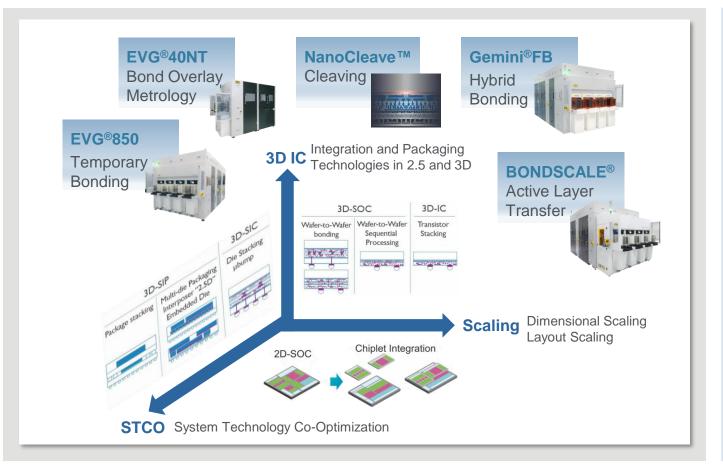

### Wafer Bonding is a Scaling Booster

- Wafer Bonding

- » Complements the traditional dimensional scaling

- Wafer-to-Wafer Hybrid Bonding:

- » Enables higher functional density at the wafer level back end

- Active Layer Transfer Fusion Bonding:

- » Exploits the wafer back side and enables front end transistor level stacking

## GAA Is Here, Now What?

**Nick Yu** Google **Custom Silicon** Technologist

Qualcomm VP of Engineering

PR Chidambaram Kevin Fischer Intel VP, Interconnect and Memory Integration

**Dong-Won Kim Geoffrey Yeap TSMC** Samsung Fellow, Logic VP, Research & Technology Development Development

**Victor Moroz Synopsys** Fellow

**Paul Lindner EV Group** Executive **Technology Director**

## **Thank You for Joining Us!**