# New Ways to Wire and Integrate Chips

MASTER CLASS May 26, 2022

#### Forward-Looking Statements and Other Information

Today's presentations contain forward-looking statements, including those regarding anticipated growth and trends in our businesses and markets, industry outlooks and demand drivers, technology transitions, our business and financial performance and market share positions, our investment and growth strategies, our development of new products and technologies, forecasts relating to our revenues, market share and other financial and business performance, and other statements that are not historical facts. These statements and their underlying assumptions are subject to risks and uncertainties and are not guarantees of future performance.

Factors that could cause actual results to differ materially from those expressed or implied by such statements include, without limitation: the level of demand for our products, our ability to meet customer demand, and our suppliers' ability to meet our demand requirements; transportation interruptions and logistics constraints; global economic, political and industry conditions, including rising inflation and interest rates; the effects of regional or global health epidemics, including the severity and duration of the ongoing COVID-19 pandemic and government imposed lockdowns and other measures taken in response; global trade issues and changes in trade and export license policies; consumer demand for electronic products; the demand for semiconductors; customers' technology and capacity requirements; the introduction of new and innovative technologies, and the timing of technology transitions; our ability to develop, deliver and support new products and technologies; the concentrated nature of our customer base; acquisitions, investments and divestitures; changes in income tax laws; our ability to expand our current markets, increase market share and develop new markets; market acceptance of existing and newly developed products; our ability to obtain and protect intellectual property rights in key technologies; our ability to achieve the objectives of operational and strategic initiatives, align our resources and cost structure with business conditions, and attract, motivate and retain key employees; the variability of operating expenses and results among products and segments, and our ability to accurately forecast future results, market conditions, customer requirements and business needs; our ability to ensure compliance with applicable law, rules and regulations; and other risks and uncertainties described in our SEC filings, including our recent Forms 10-Q and 8-K. All forward-looking statements are based on management's current estimates, projections and assumptions, and we assume no obligation to upda

Applied Materials, the Applied Materials Logo, and other trademarks so designated as product names are trademarks of Applied Materials, Inc. Other names and brands are the property of third parties.

## 2022 MASTER CLASSES WELCOME

#### Michael Sullivan

Corporate Vice President Head of Investor Relations

NEW WAYS TO WIRE AND INTEGRATE CHIPS MASTER CLASS | MAY 26, 2022

#### 2022 Master Classes

APRIL 21

New Ways to Shrink

MAY 26

New Ways to Wire and Integrate Chips

| 9:00 | PART 1 | Mike Sullivan Introduction and Fireside Chat with Regina Freed                                                                                                                                                                                    |

|------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 9:05 | PART 2 | Kevin Moraes, Ph.D. Solving the Resistance Challenges of EUV Scaling  Mehul Naik, Ph.D. Enabling Backside Power Distribution Networks  Sundar Ramamurthy, Ph.D. Enabling Heterogenous Chip Integration with Hybrid Bonding and Advance Substrates |

|      |        | Develop A charther are Db D                                                                                                                                                                                                                       |

| 9:45 | PART 3 | Raman Achutharaman, Ph.D.  Growth in Chip Wiring and Integration                                                                                                                                                                                  |

| 9:50 | PART 4 | Q&A<br>Mehul, Sundar, Raman, Mike                                                                                                                                                                                                                 |

#### 2022 Master Classes

APRIL 21

New Ways to Shrink

MAY 26

New Ways to Wire and Integrate Chips

Sept 22\*

Subscriptions and Services

<sup>\*</sup> Target date

Regina Freed

Vice President

Semiconductor Products Group

## Solving the Resistance Challenges of EUV Scaling

Kevin Moraes, Ph.D.

Vice President

Semiconductor Products Group

NEW WAYS TO WIRE AND INTEGRATE CHIPS MASTER CLASS | May 26, 2022

#### Creating Amazing Digital Experiences with Billions of Transistors

#### Brought to you by:

- 1. Low-resistance wiring

- 2. Backside power distribution networks

- 3. Heterogenous integration

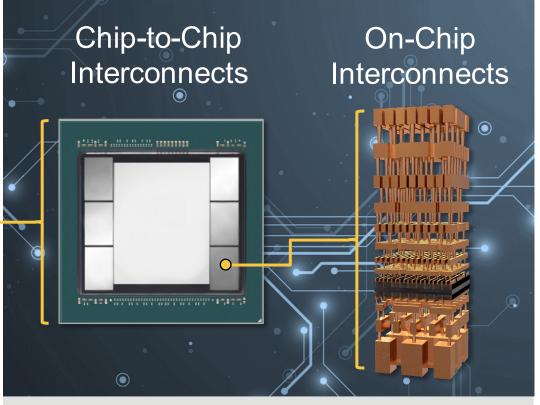

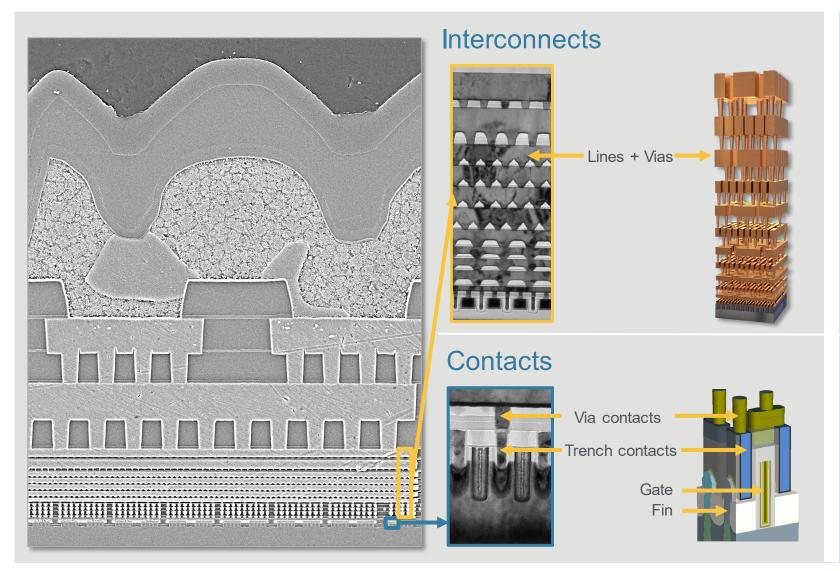

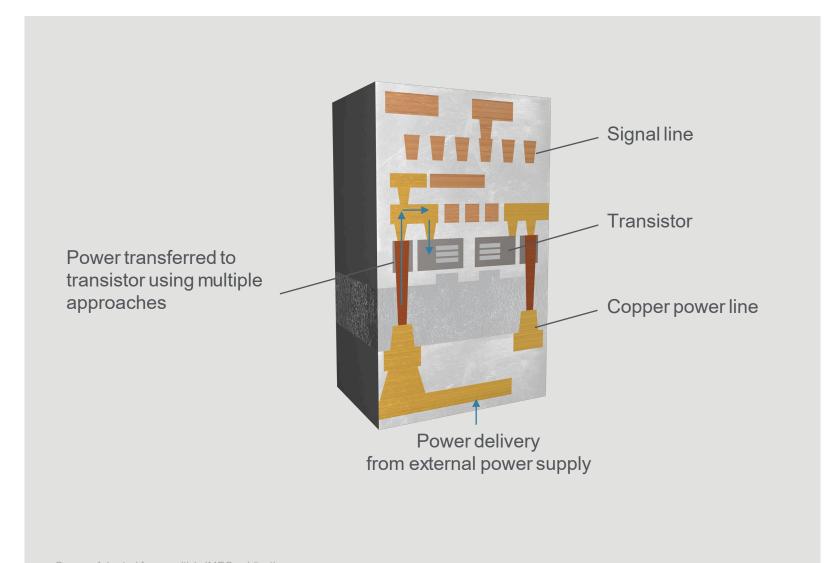

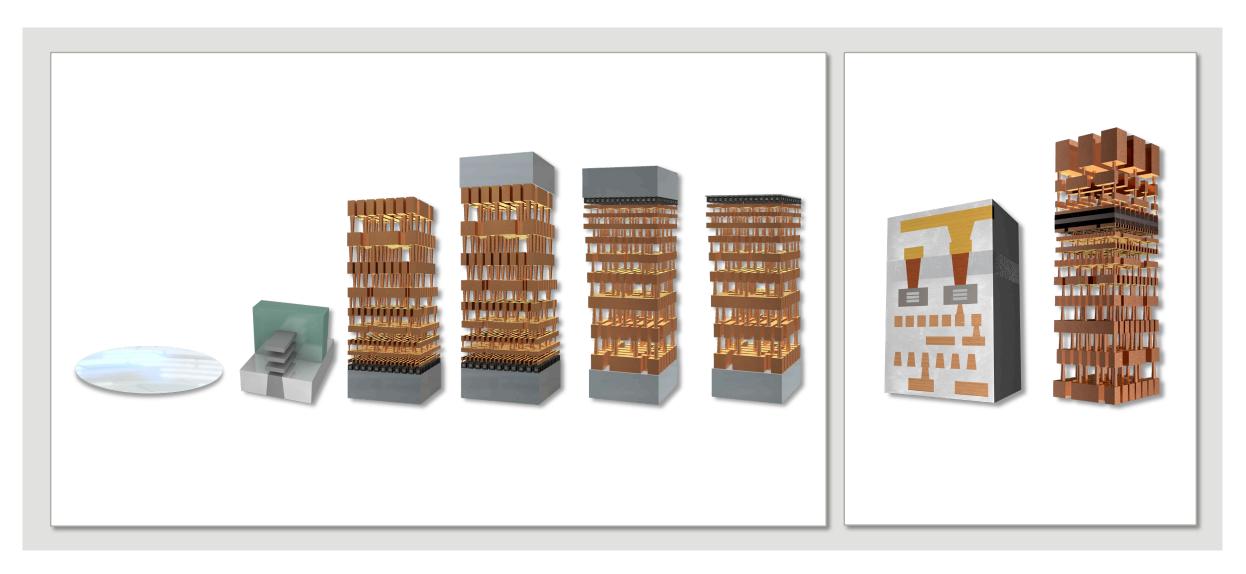

### Wiring Transistors On a Chip

- Make connections laterally and vertically

- Over 15 metal layers

- 4-5 layers at minimum pitch

- Smallest widths ~14nm

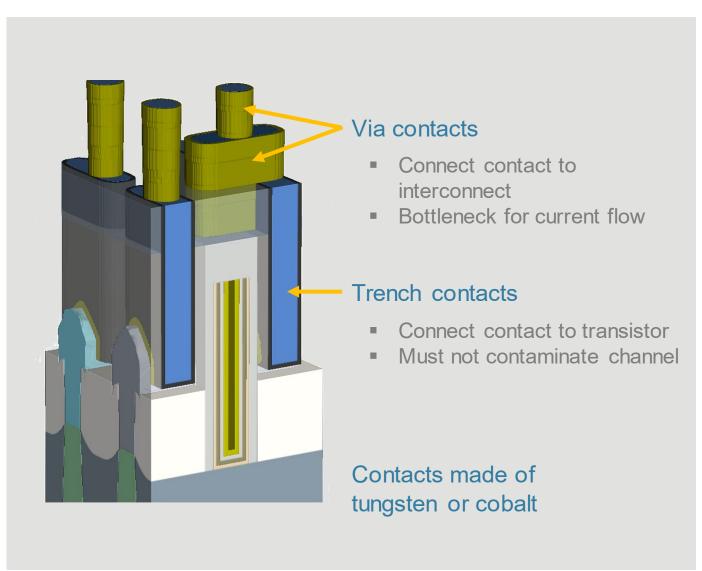

- Connect transistors to interconnects

- One or two metal layers

- Smallest widths ~12nm

Image source: TechInsights and Applied Materials

#### **Creating Transistor Contacts**

#### Creating Interconnects Between Transistors

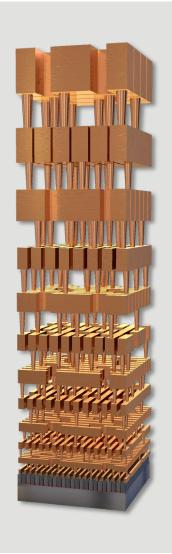

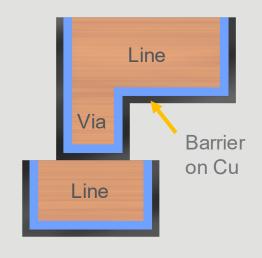

#### Interconnects

Lines make lateral connections within each layer; vias connect layers

Chips have >50 miles of copper interconnect wiring

Resistance impacts power and performance

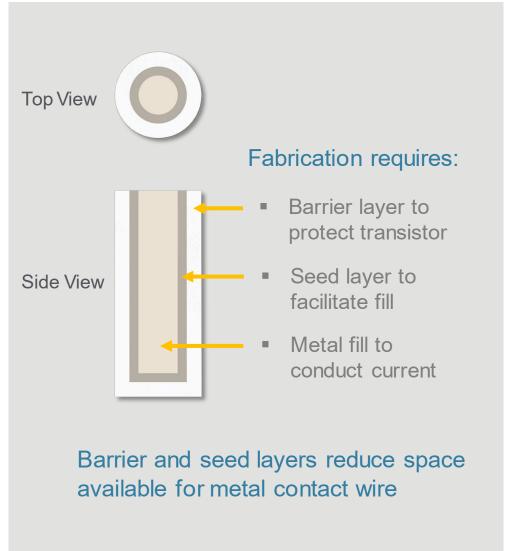

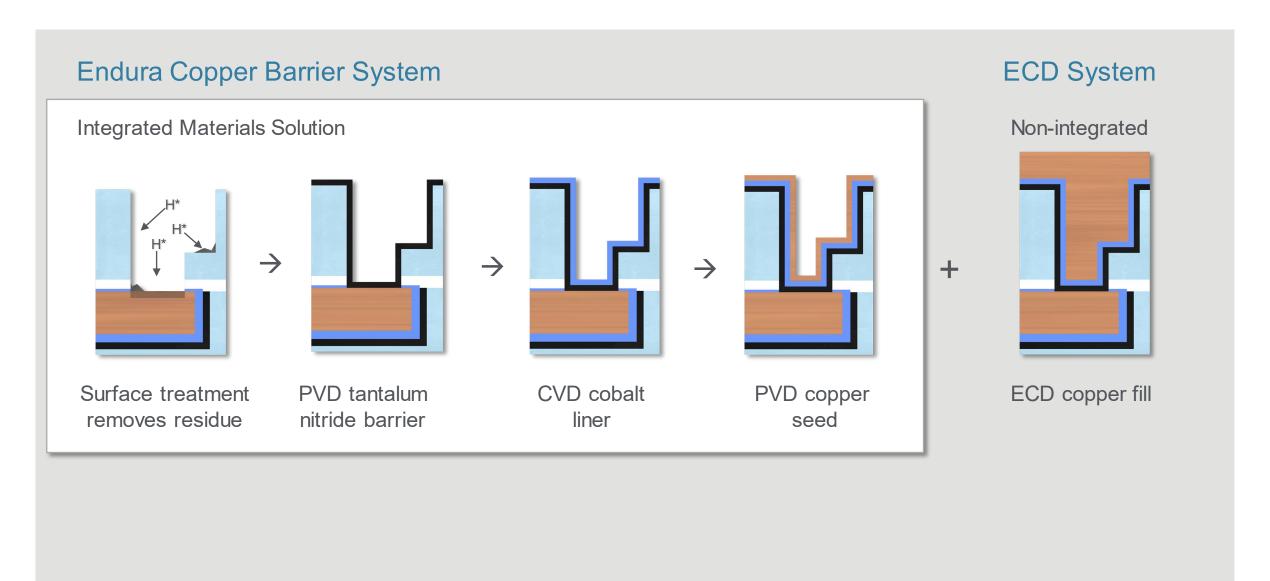

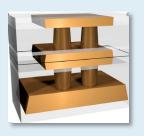

#### Fabrication requires:

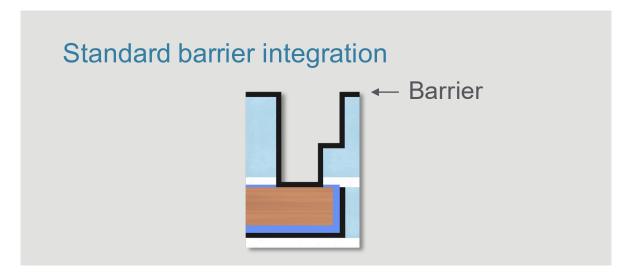

- Barrier to block copper diffusion

- Liner to improve copper adhesion

- Seed layer for copper growth

- Copper fill to complete wire

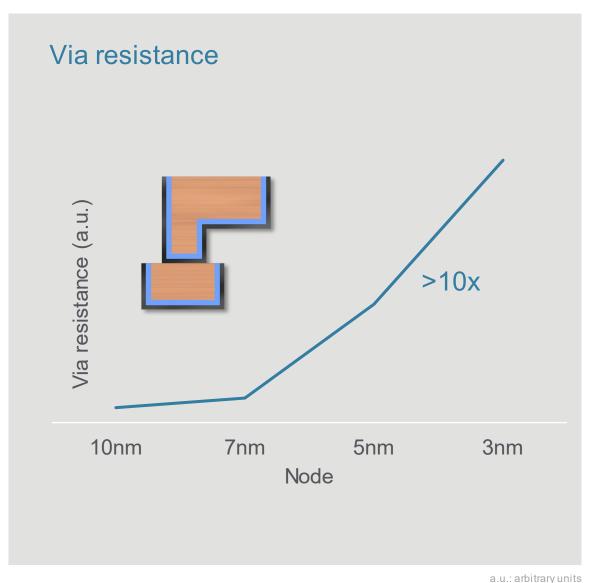

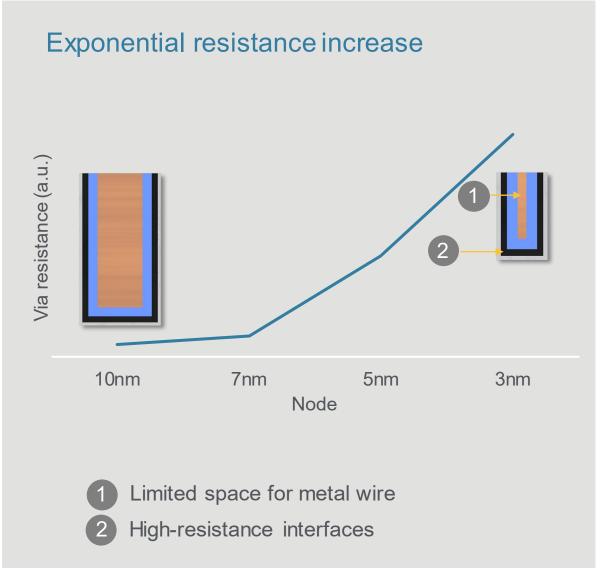

Barrier layers increase via resistance, cause RC delays, waste power

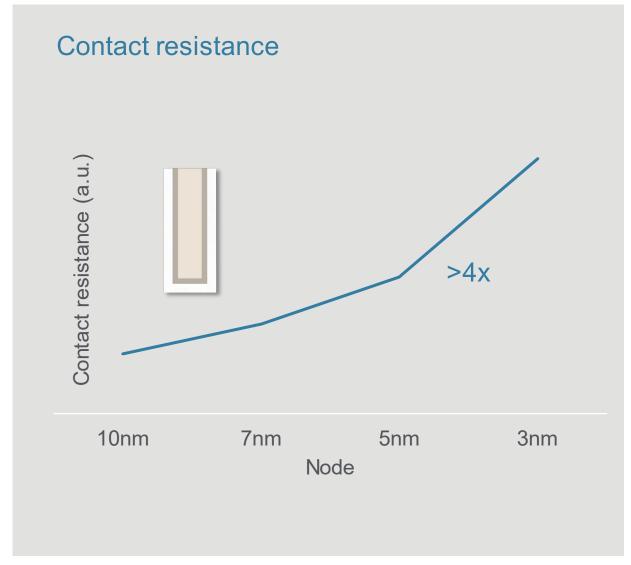

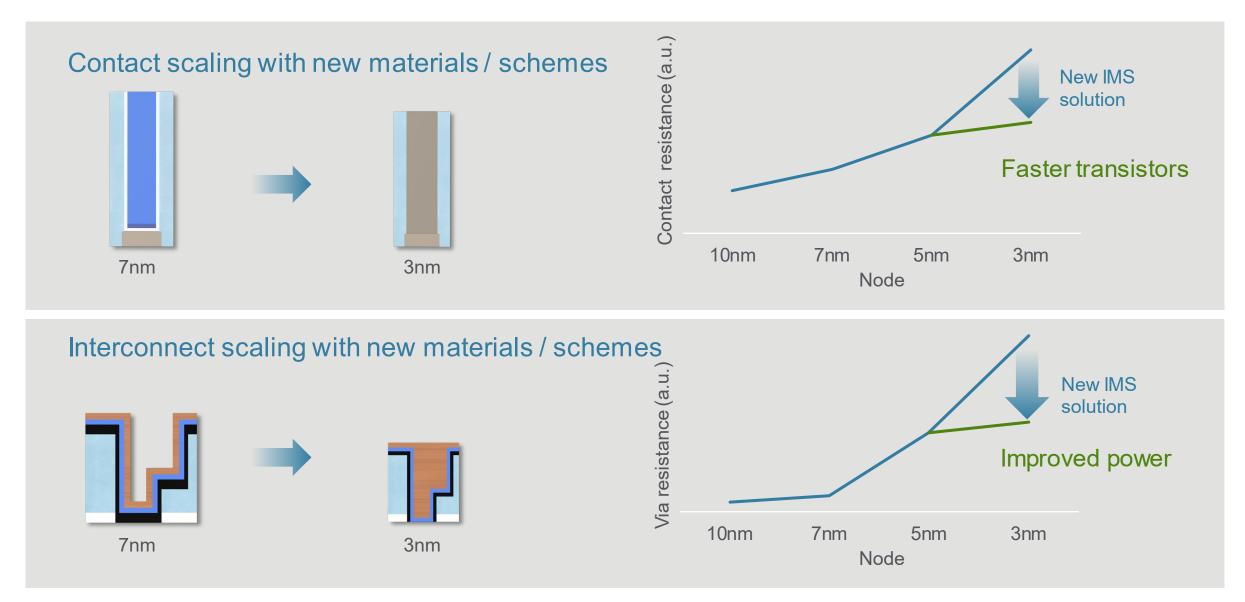

### Resistance Increases Exponentially as Wiring Scales

Assumptions: Dimensions scale; liner/barrier materials and dimensions do not

#### **Contact Resistance Innovations**

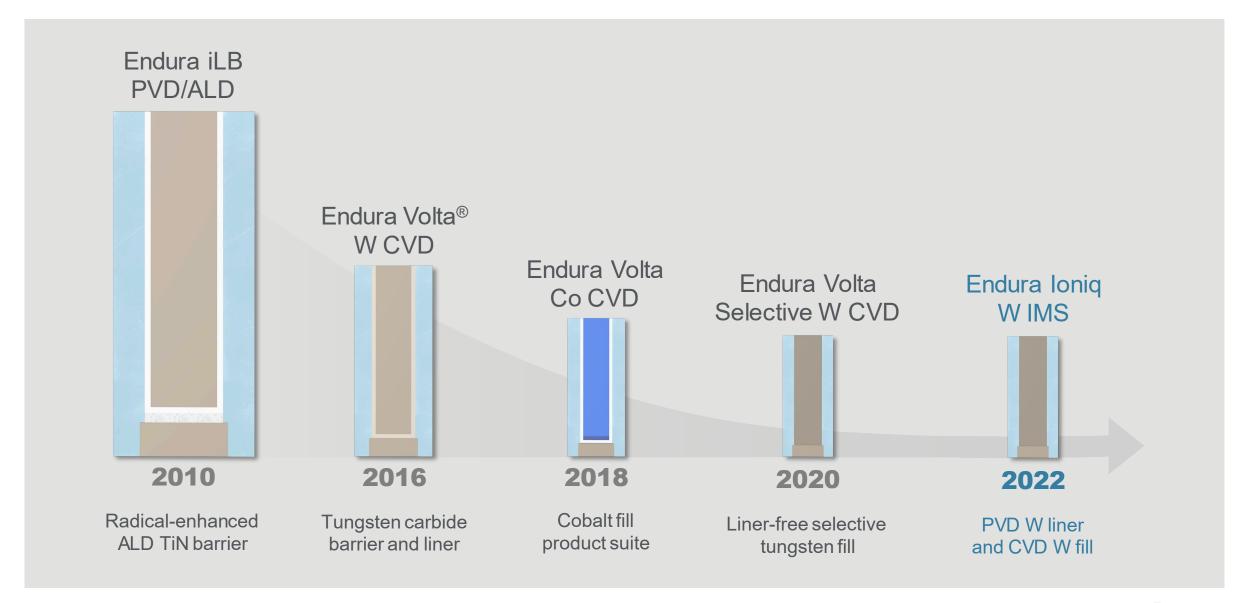

### Endura Ioniq<sup>™</sup> W PVD: Low-Resistance Tungsten Contacts

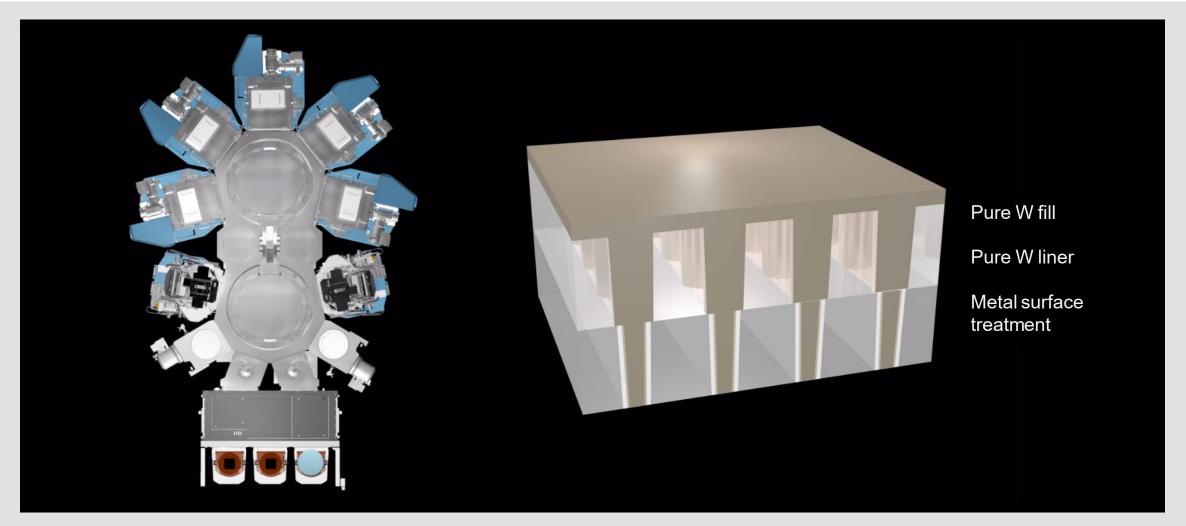

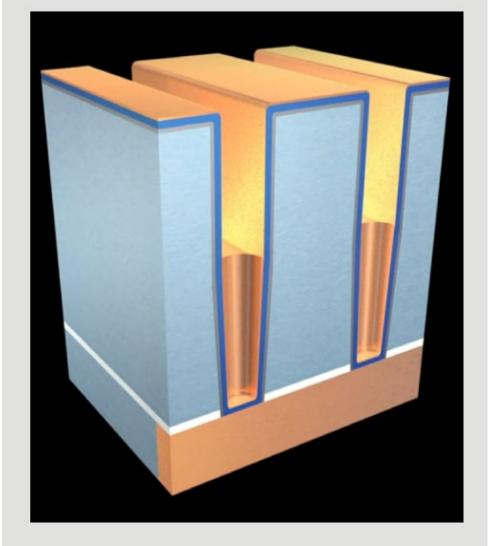

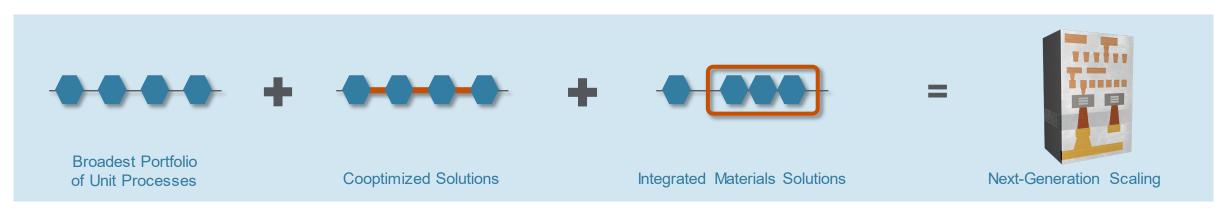

## Integrated Materials Solution<sup>™</sup> for pure tungsten metal gapfill

- Combines interface engineering, PVD and CVD in high-vacuum

- Enables contact scaling in a wide variety of applications

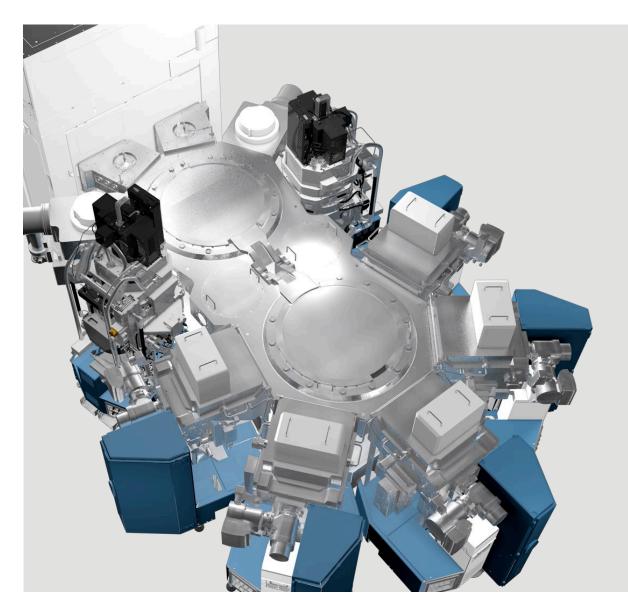

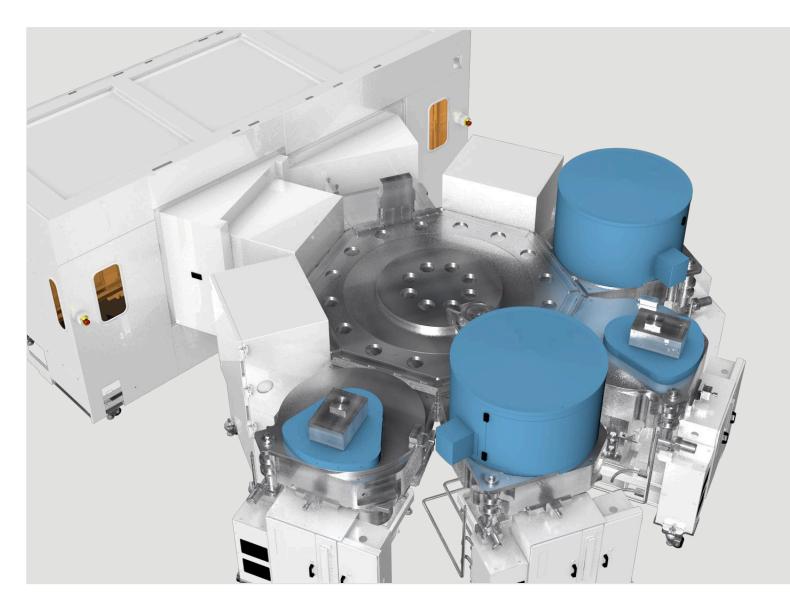

## Endura Contact Metal IMS™ System

Integrated Materials Solution Enables Pure Metal Contacts

#### **Contact Resistance Innovations Continue**

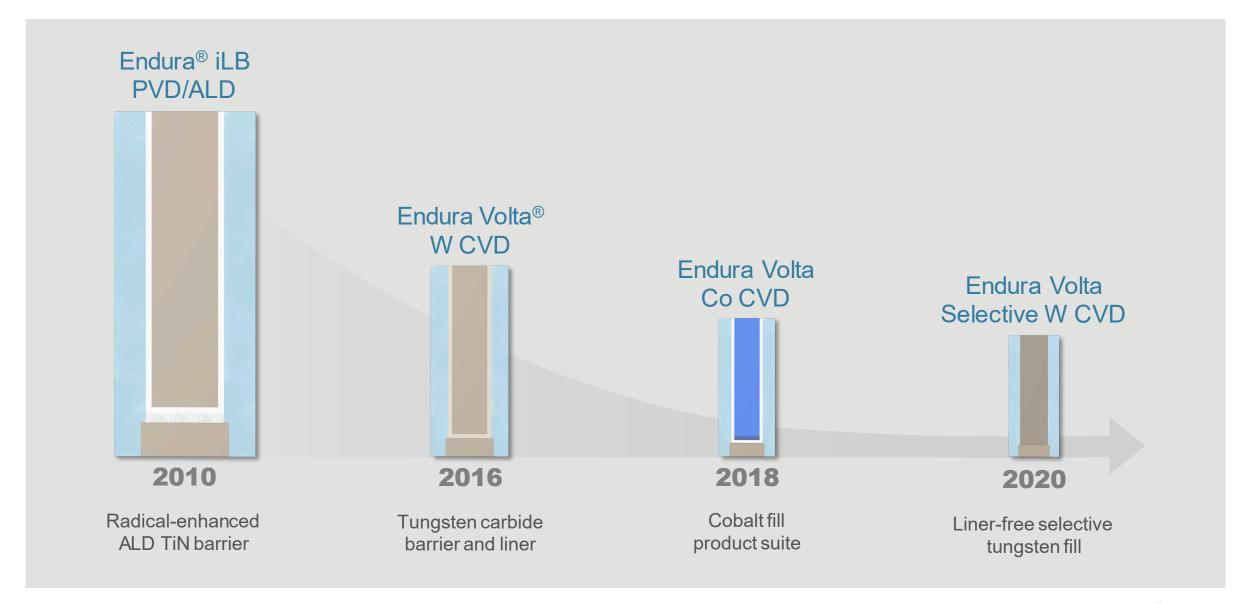

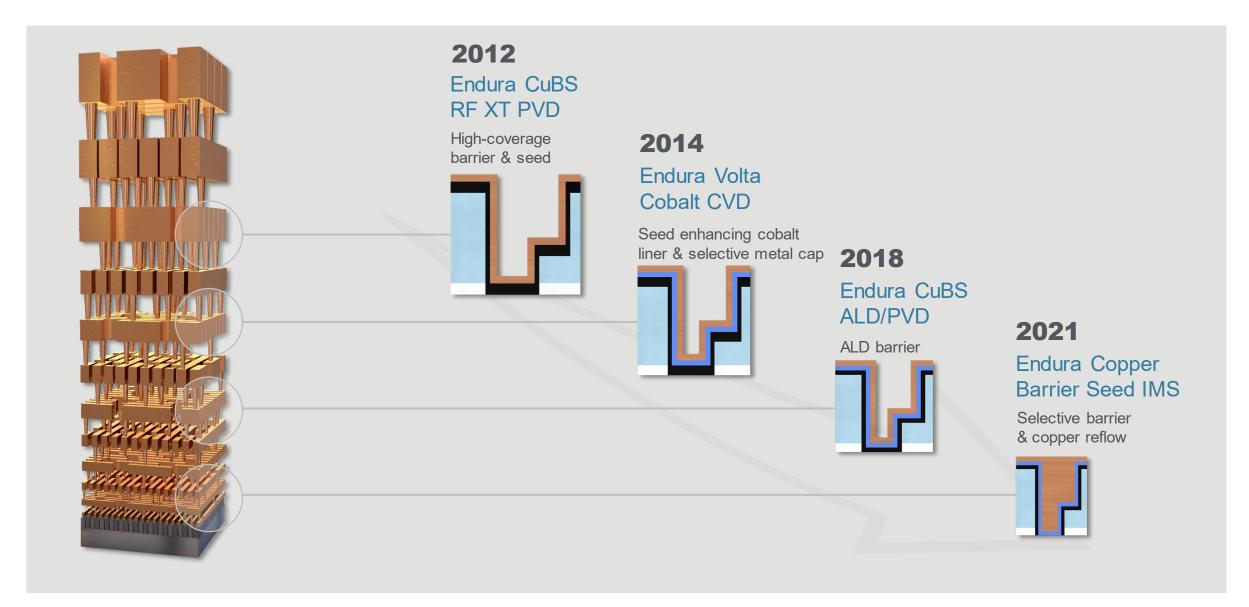

## Innovations to Extend Copper Interconnects

### Copper Interconnect Fabrication

#### Challenges Extending Copper Interconnects at 5nm

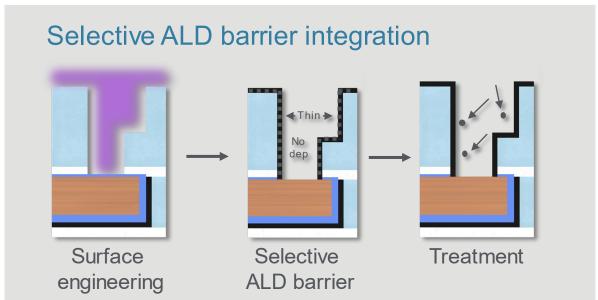

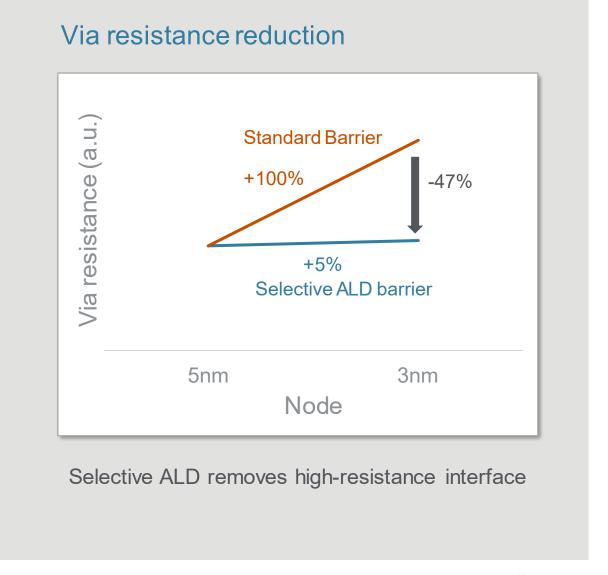

#### Lowering Via Resistance with Selective ALD Barriers

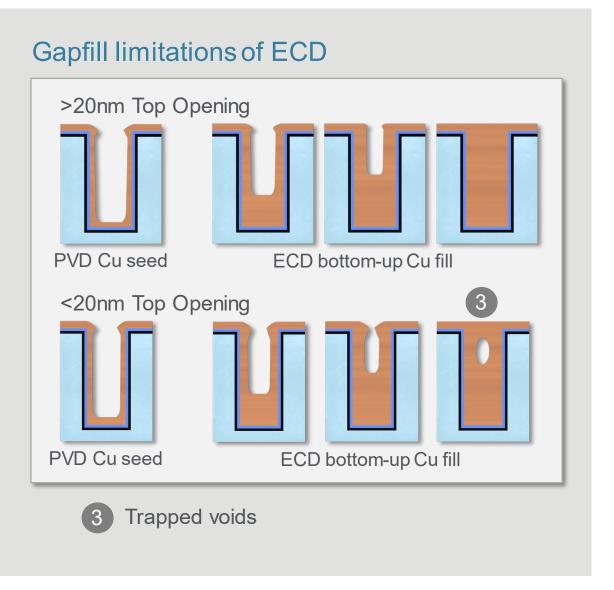

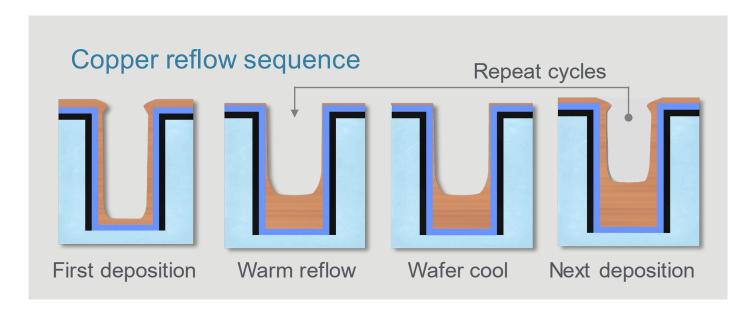

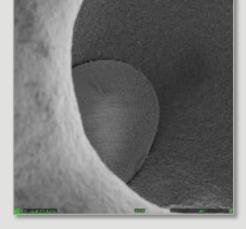

### Reliable Copper Gapfill with PVD Copper Reflow

#### Complete fill with PVD copper reflow

## Unique IMS Solutions Address Resistance Issues of EUV Scaling

## Enabling Backside Power Distribution Networks

#### Mehul Naik, Ph.D.

Managing Director and Principal Member of Technical Staff Semiconductor Products Group

NEW WAYS TO WIRE AND INTEGRATE CHIPS MASTER CLASS | May 26, 2022

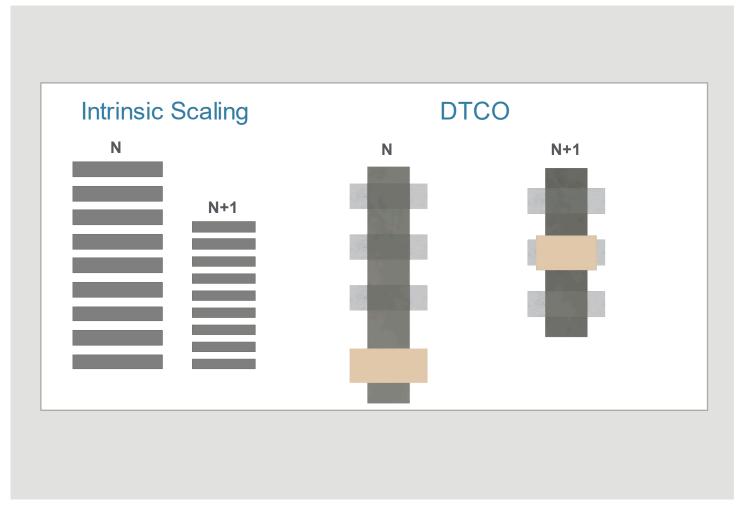

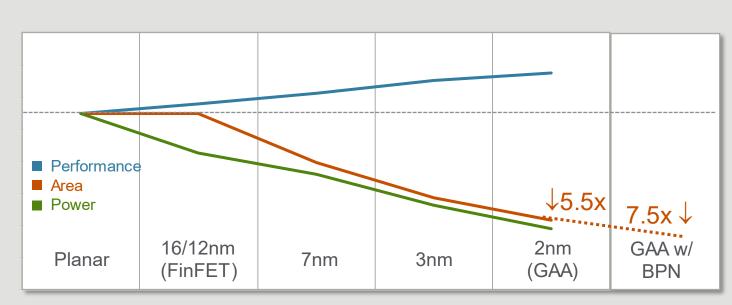

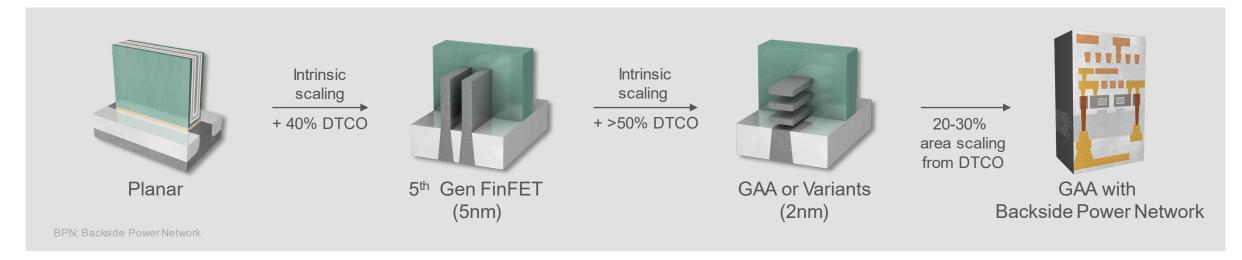

#### **Device Scaling Approaches**

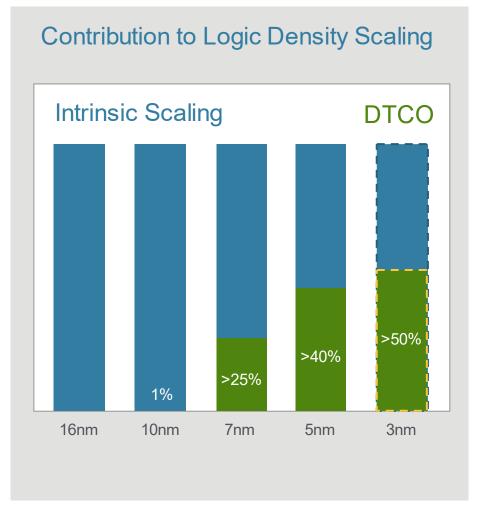

Source: M. Liu/TSMC, ISSCC 2021

DTCO: Design Technology Co-Optimization

DTCO is becoming an increasingly important contributor to scaling

### Future of Logic Scaling

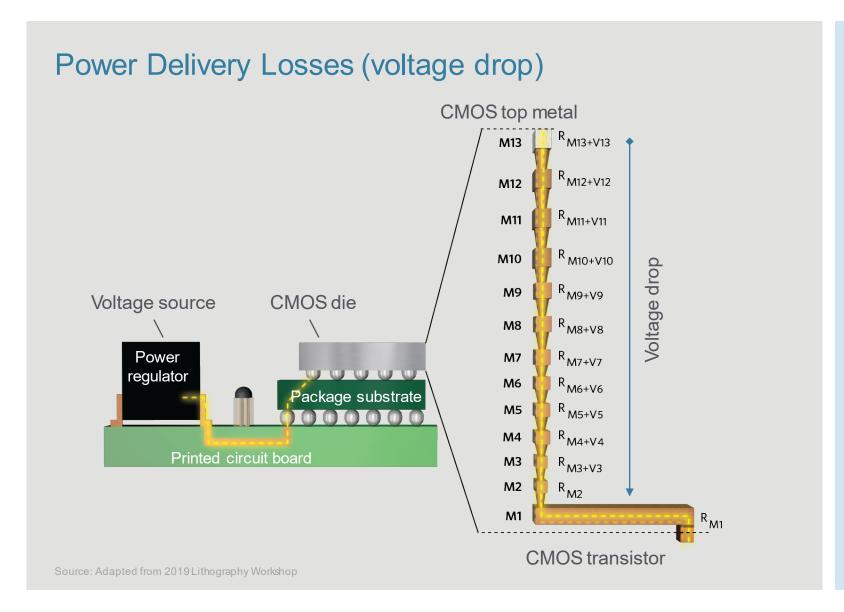

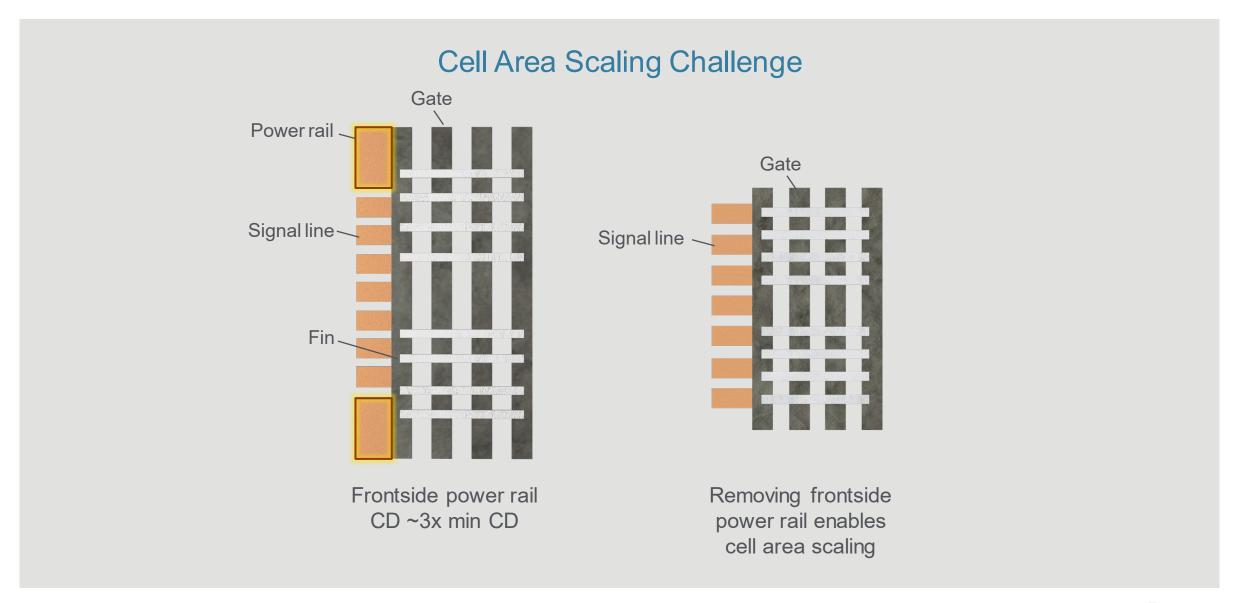

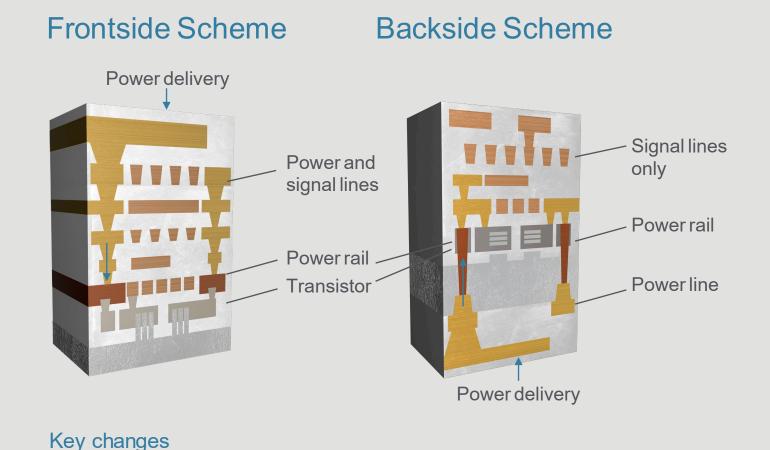

#### Limitations of Frontside Power Distribution Network Architecture

- Power delivery network design margin permits 10% IR drop

- Large IR drop from 12+ metal levels due to resistance

- Excessive IR drop

(~50%) creates reliability

issues

#### Limitations of Frontside Power Distribution Network Architecture

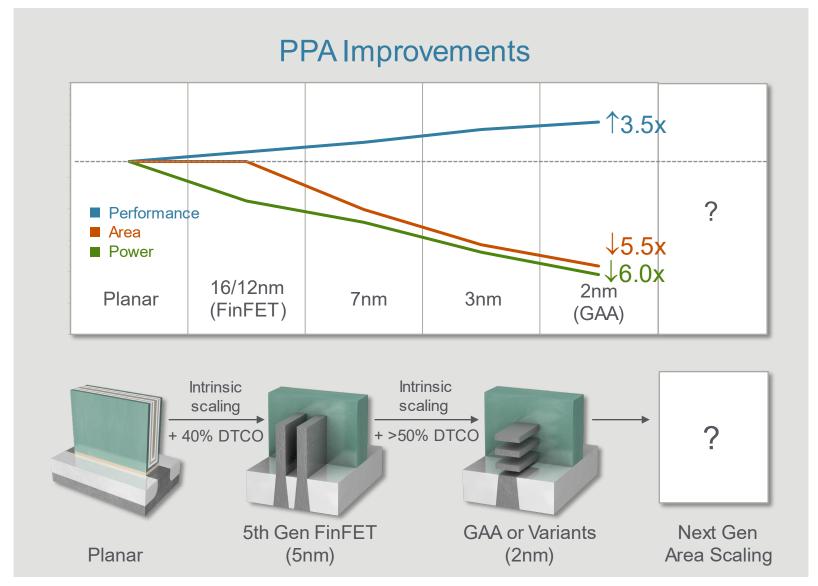

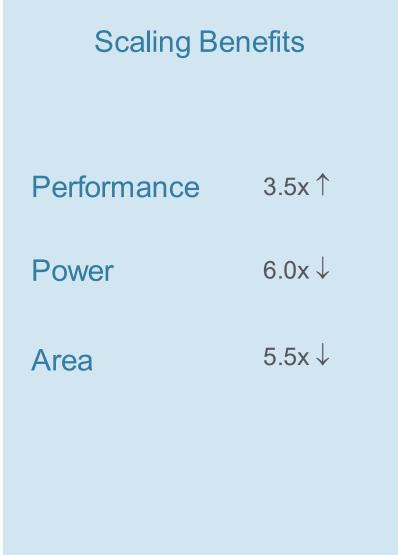

#### PPACt Benefit of Backside Power Distribution Network Inflection

Reduced Maintain 10% design margin Voltage Drop

Area Savings

20 to 30% cell area reduction

- Separation of power and signal lines

- Power delivery from backside of the wafer

Source: Adapted from multiple IMEC and ARM publications

### GAA with Backside Power Network for Additional Area Scaling

20 to 30% cell area reduction with Backside Power Network

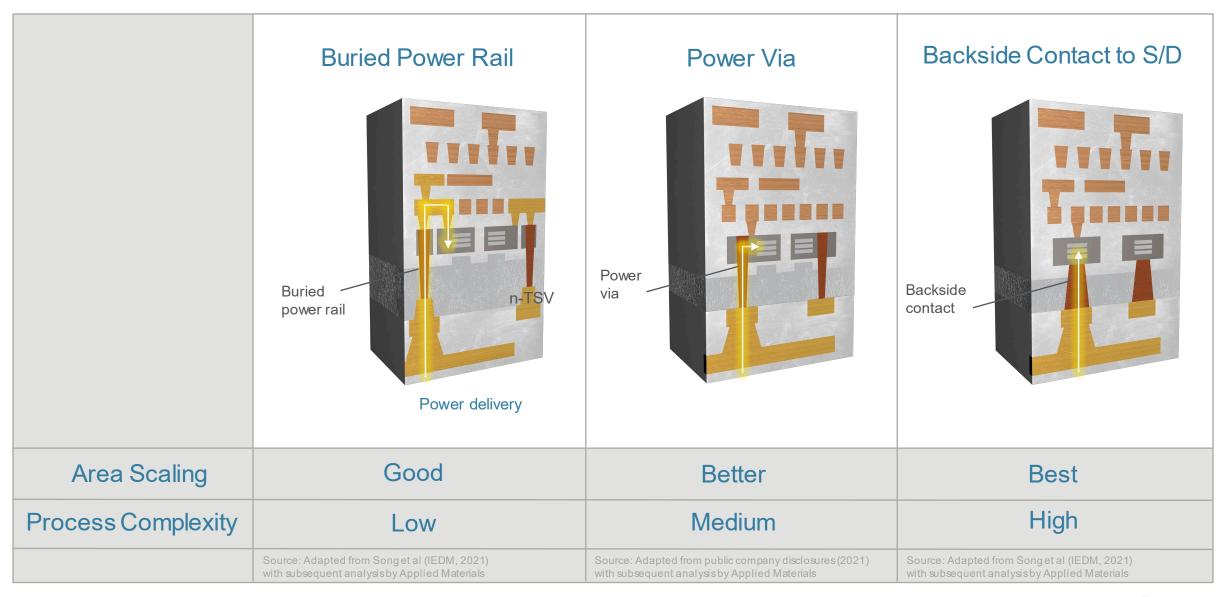

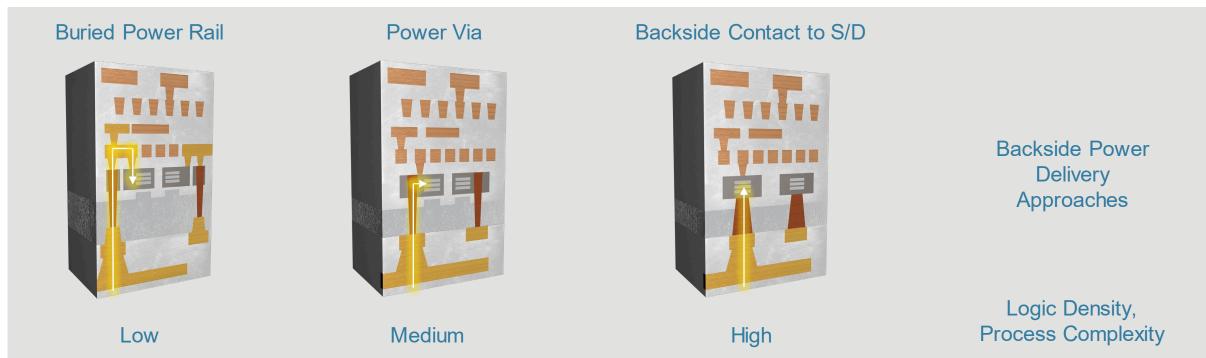

#### Backside Power Distribution Network Architecture

- Multiple approaches in development

- Trade-offs between power/area scaling and manufacturing complexity

Source: Adapted from multiple IMEC publications

#### Announced Backside Power Distribution Network Approaches

#### Frontside and Backside Wafer Fabrication

#### Broad Portfolio Addresses all Backside Power Distribution Schemes

#### Frontside and Backside Wafer Fabrication

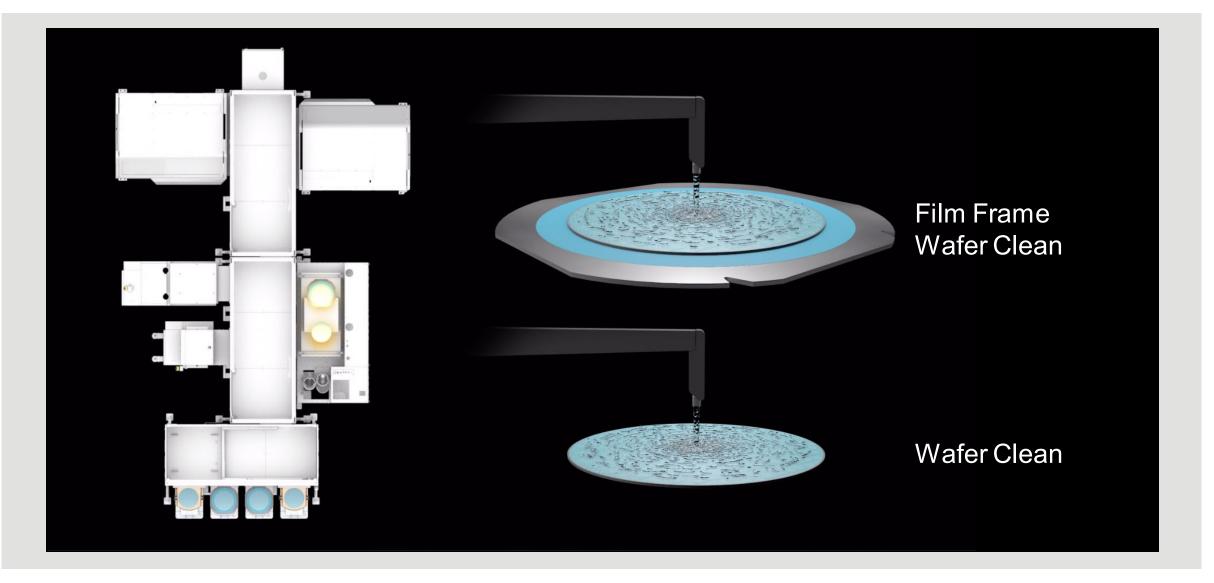

Utilizing the backside of wafer for power delivery

## New Ways to Integrate Chips

#### **Sundar Ramamurthy**

Group Vice President, GM Semiconductor Products Groups

NEW WAYS TO WIRE AND PACKAGE CHIPS MASTER CLASS | May 26, 2022

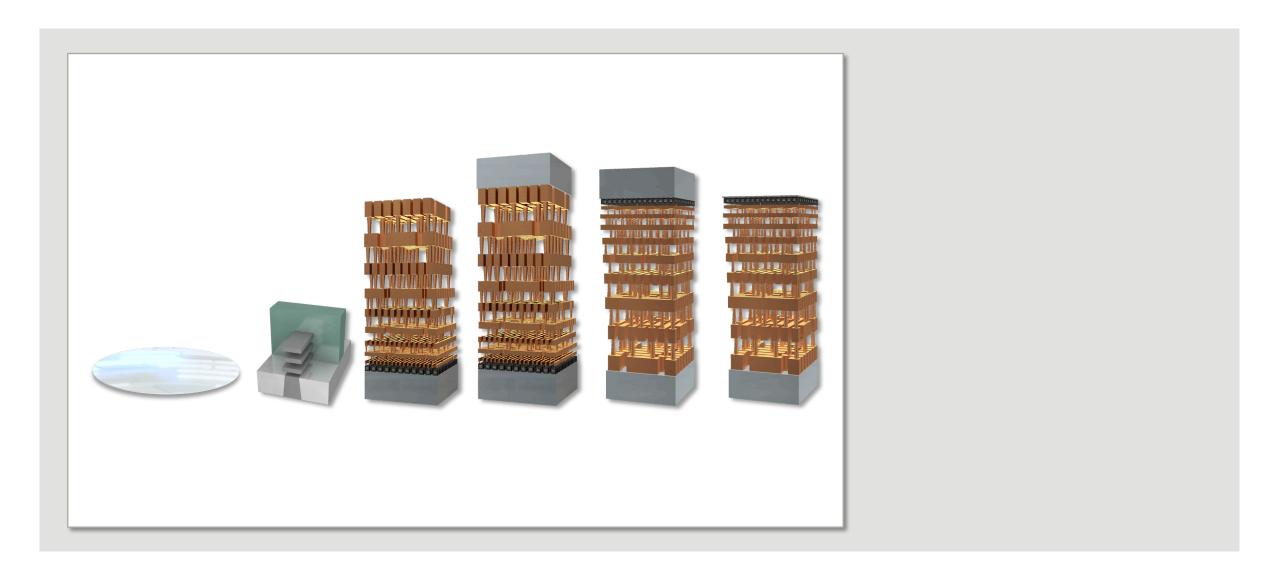

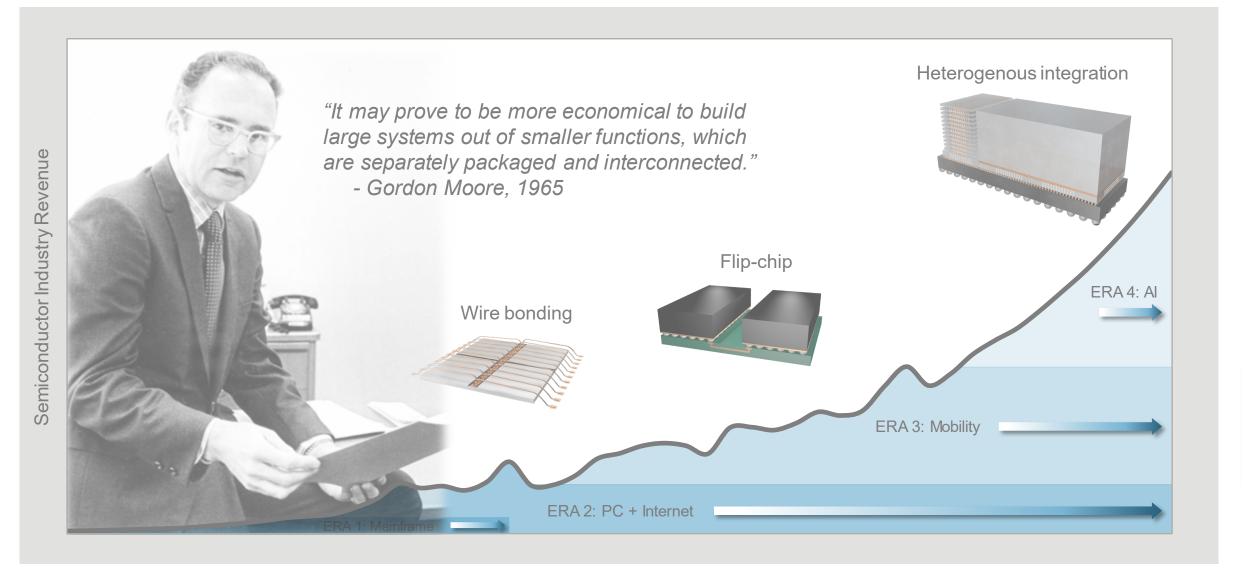

# Heterogeneous Chip Design – An Evolution of Moore's Law

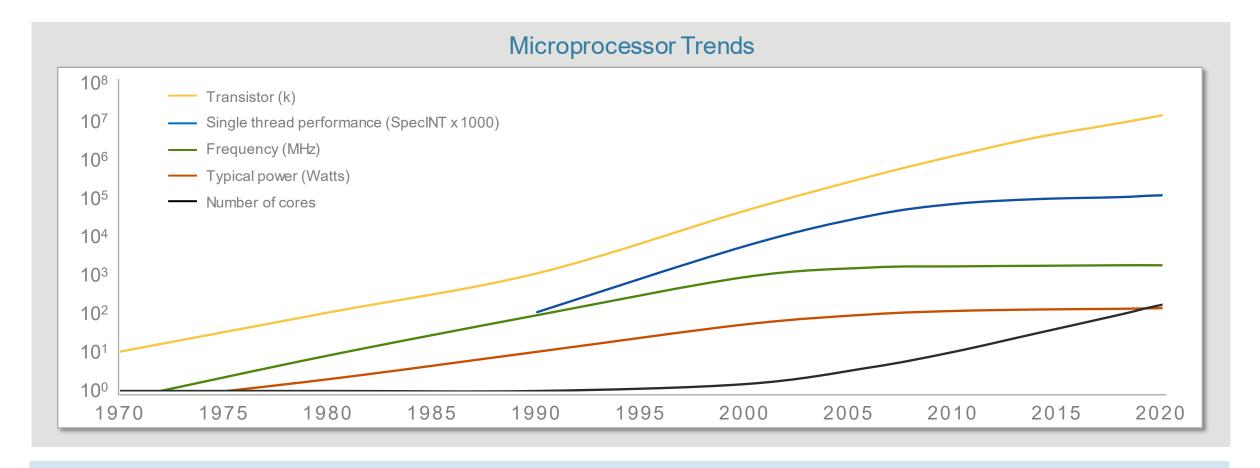

#### Traditional Moore's Law Scaling Hits Limits

- Single-threaded processor performance has plateaued despite increases in cores and transistors

- Application accelerator performance continues to scale with cores and transistors

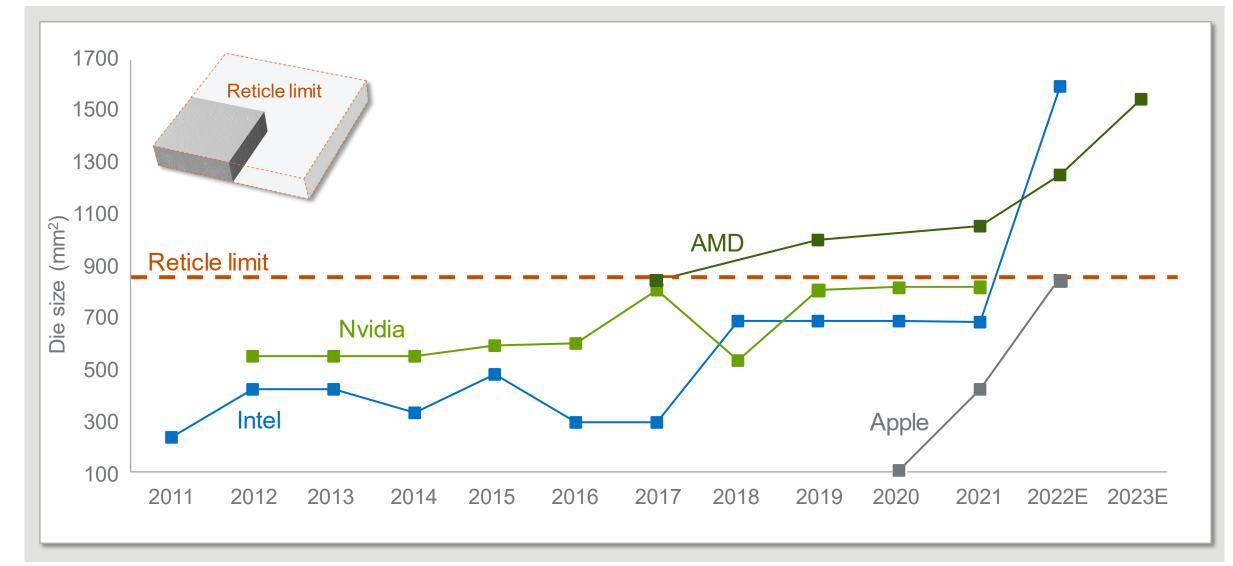

#### Transistor Counts are Hitting the Reticle Limit

Source: Jefferies

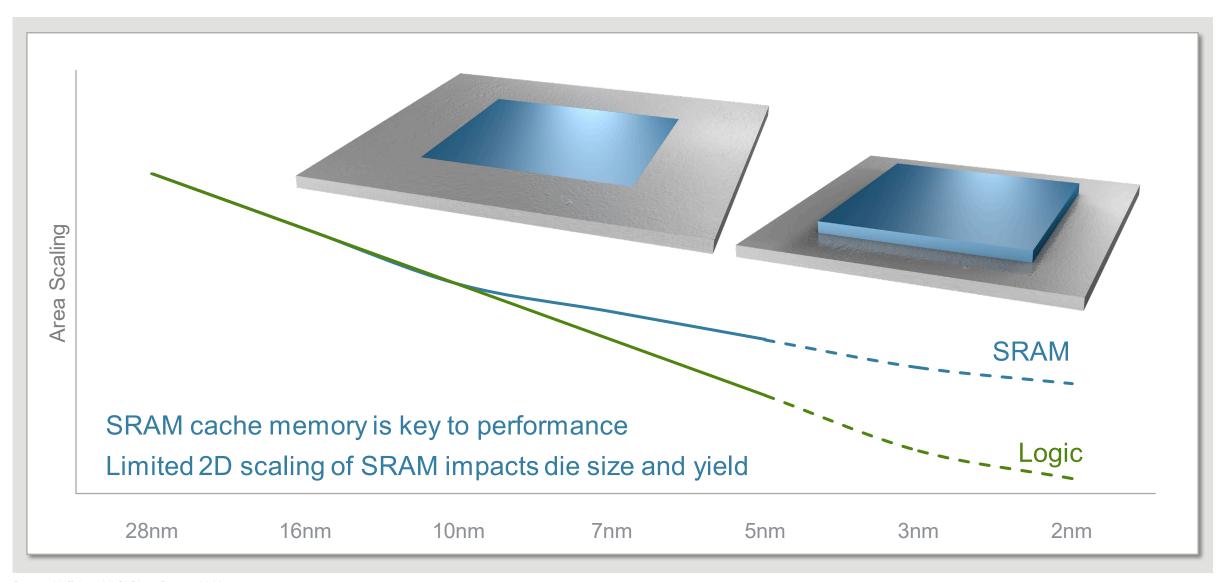

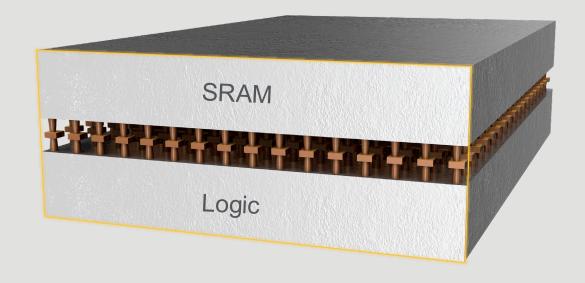

#### Opportunity: Heterogeneous SRAM Integration

Source: Naffziger, VLSI Short Course, 2020

Source : Yole Développement Applied Materials External

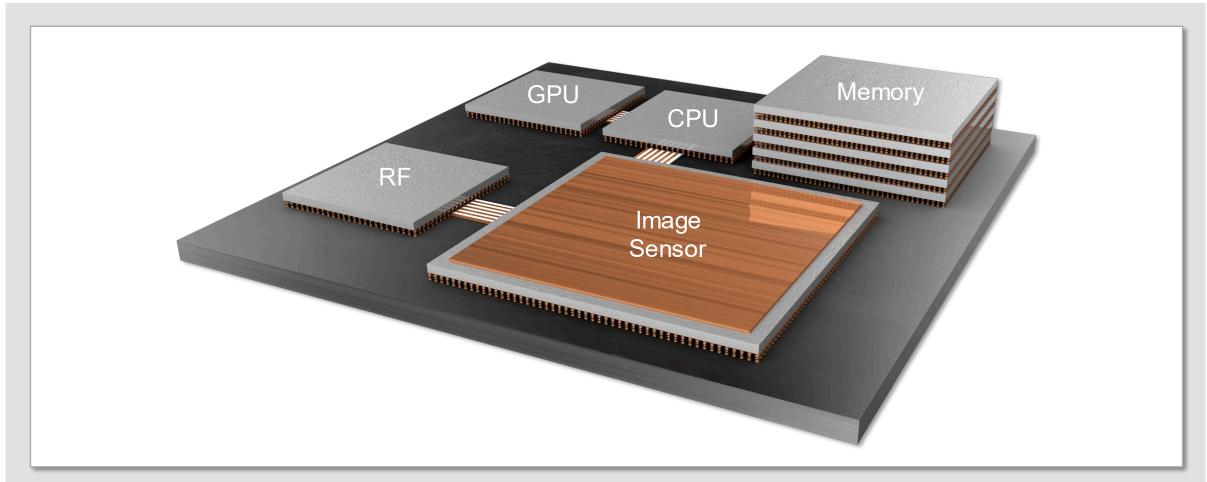

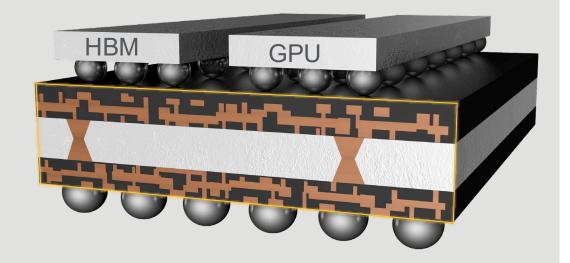

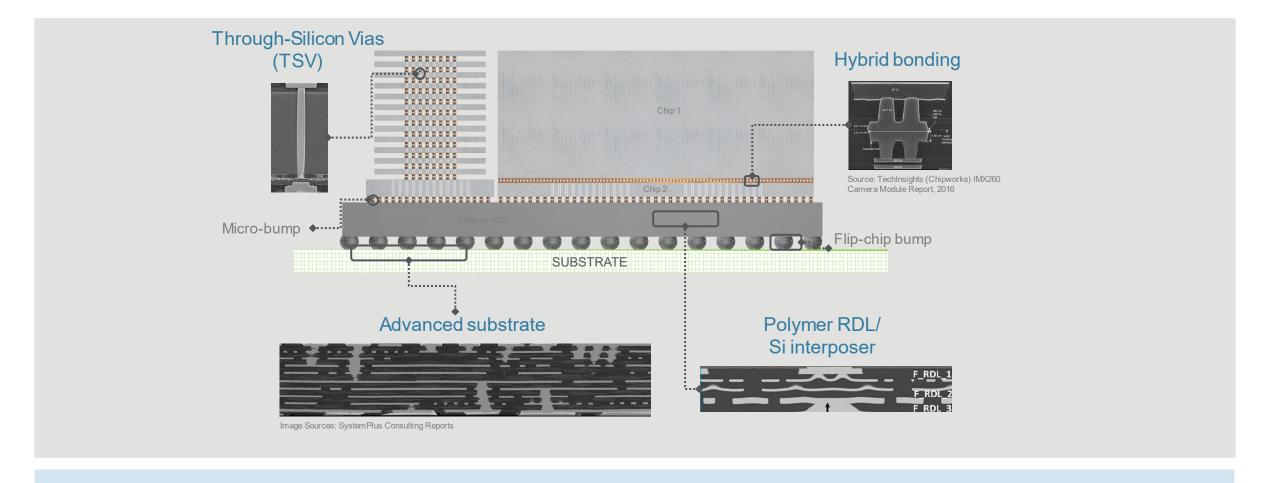

### Heterogenous Integration to the Rescue

Heterogeneous integration enables logic, memory, sensors, power and communications to be combined as a system-in-package

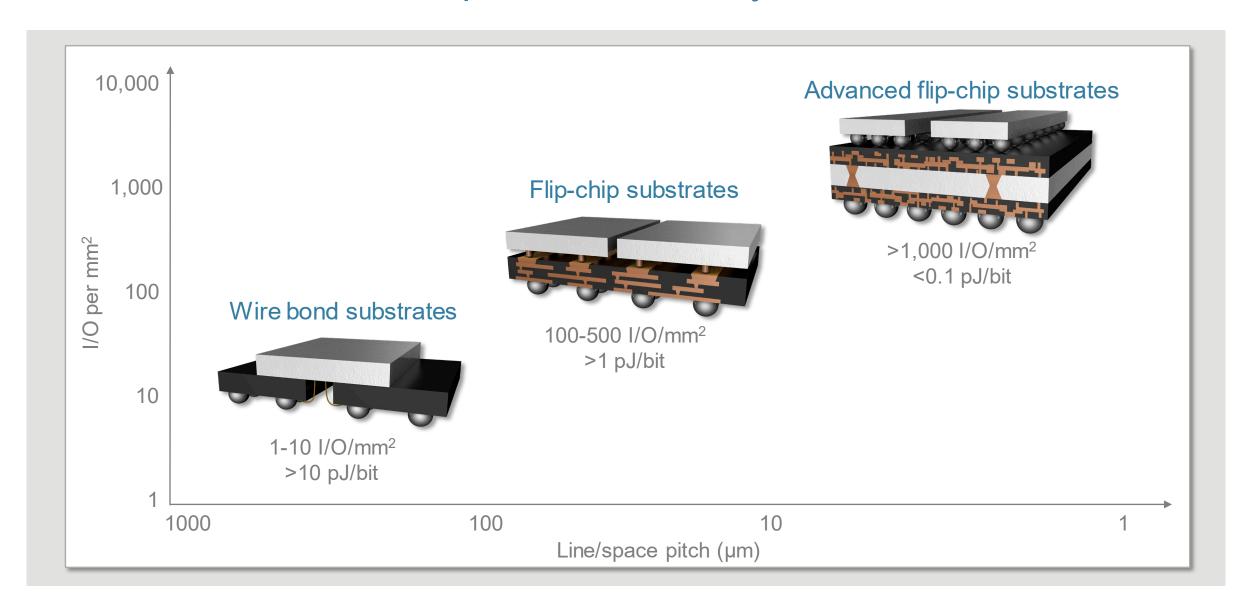

### Advanced Interconnects Enable "System-in-Package" Era

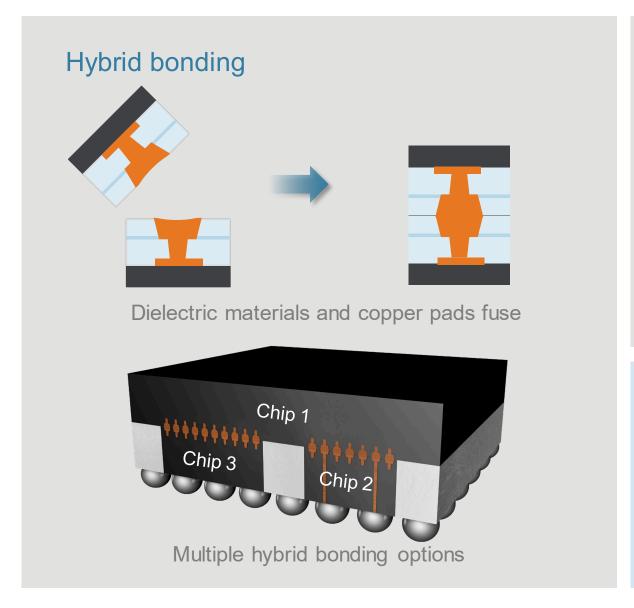

#### Hybrid bonding

Hybrid bonding enables up to >10,000 I/Os per mm<sup>2</sup>

#### Advanced substrates

Advanced substrates connect multiple high-performance die at high I/O density and data bandwidth

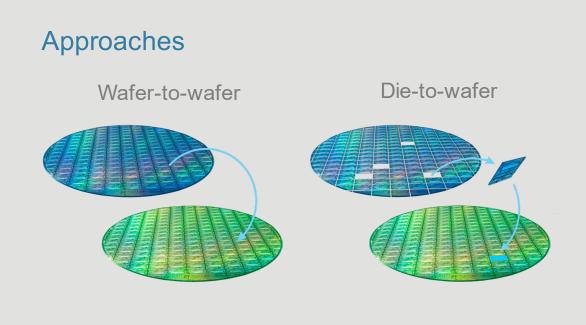

### Hybrid Bonding for High-Density Chip-to-Chip Interconnects

- Enables >10,000 connections per mm<sup>2</sup>

- Requires precision in processing and alignment

- SoC performance can be reconstituted and expanded with hybrid bonded chiplets

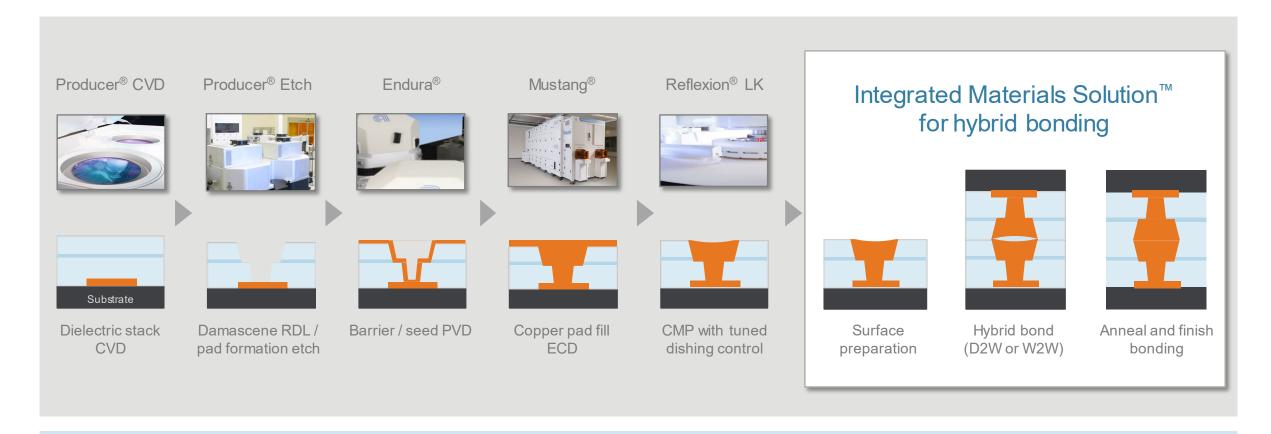

### End-to-End Portfolio of Hybrid Bonding Solutions

- Collaborating with partners to develop end-to-end technologies to ramp hybrid bonding solutions

- Center of Excellence investigates materials and process interactions on custom test vehicles

CVD: Chemical Vapor Deposition

PVD: Physical vapor deposition

RDL: Redistribution laver

## Integrated Materials Solution for Chip-to-Wafer Hybrid Bonding

#### Advanced Substrates Improve I/O Density and Power

#### System Integration with Emerging 2D and 3D Interconnects

- Advanced substrates package chips side-by-side with higher bandwidth (more I/Os) and lower power

- TSVs with micro-bumps or hybrid bonding create vertical interconnects allowing chip-on-chip stacking

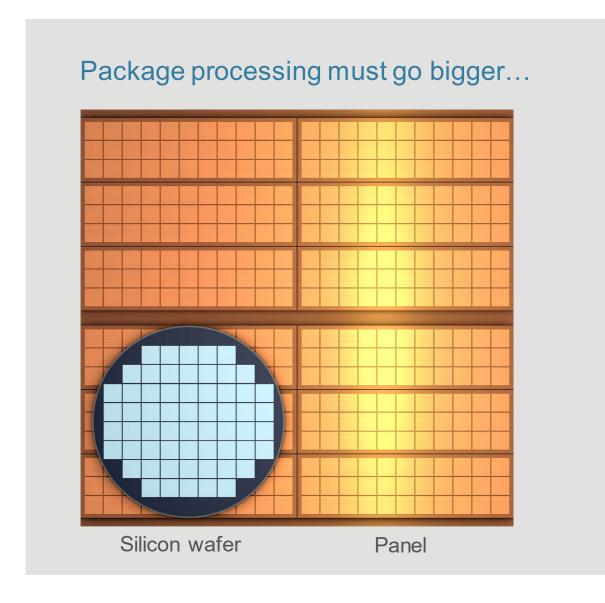

#### Quest for Performance is Making Packages Larger

- Multiple chiplets in a package

- Package areas as large as 10,000mm<sup>2</sup>

- Round wafers have poor area efficiency

Panels enable greater number of larger packages

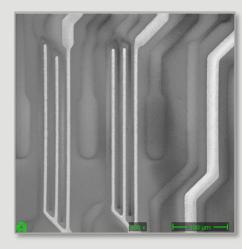

### Semiconductor-Grade Large Substrate Processing

#### Applied Topaz<sup>™</sup> PVD System

- Substrates up to 600x600mm

- Cluster chamber architecture

- Multiple applications supported

Creating an industry ecosystem for semiconductor-grade panel-level packaging

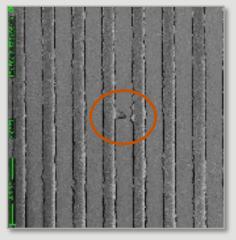

### Panel-Level eBeam Metrology and Test

#### Defect review with SEM and FIB analysis

Protrusion

Residuals

#### Non-destructive eBeam test

Shorts highlighted

- Automatic defect review

- Precise CD measurement

- In-situ failure analysis

- Fault detection by voltage contrast

- High-throughput analysis

- Damage-free

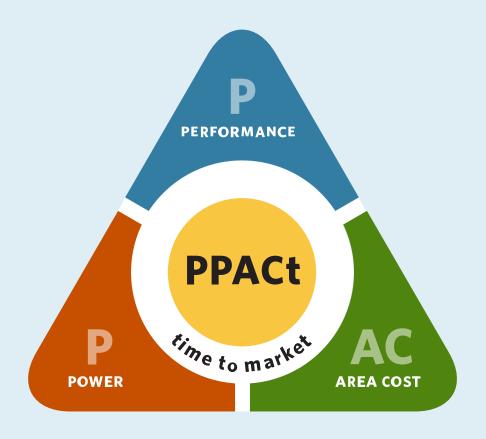

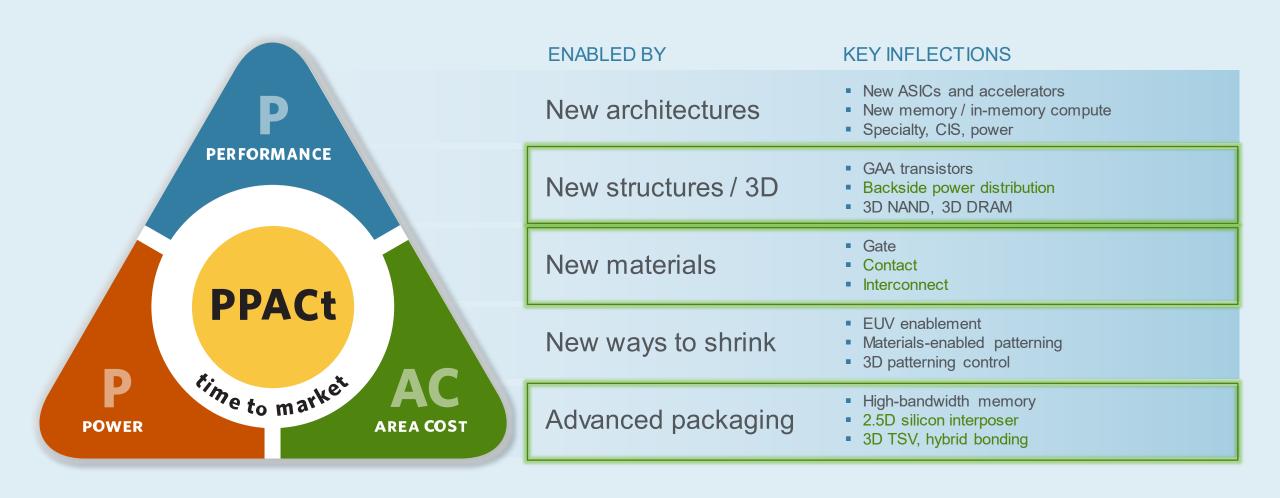

### Wiring & Heterogenous Integration Enable PPACt™ Scaling

Low-resistance contacts and interconnects

- P Lower power loss

- P Faster switching

40-50% resistance reduction @ 3nm with IMS™

# Backside power distribution networks

- Increased logic scaling

- P Lower power loss

Up to 30% logic density improvement vs. frontside power

# Hybrid bonding and advanced substrates

- Heterogenous integration

- P Higher I/O and bandwidth

- P Lower power loss

Enables >10,000 I/Os per mm<sup>2</sup> and packages as large as 10,000mm<sup>2</sup>

IMS: Integrated Materials Solution

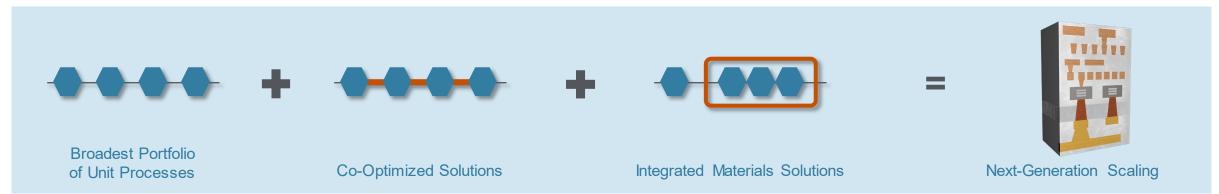

# Growth in Chip Wiring and Integration

#### Raman Achutharaman, Ph.D.

Group Vice President

Semiconductor Products Group

NEW WAYS TO WIRE AND INTEGRATE CHIPS MASTER CLASS | May 26, 2022

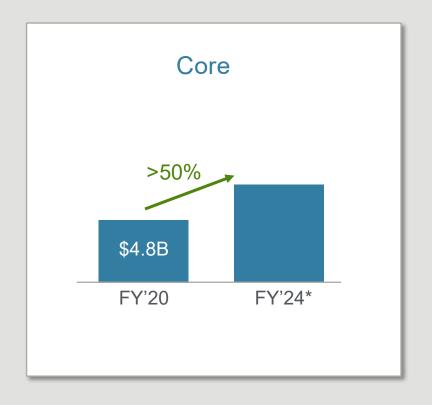

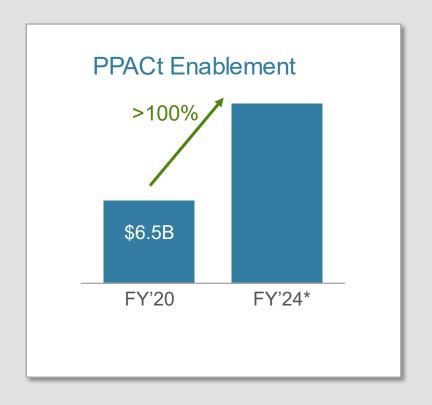

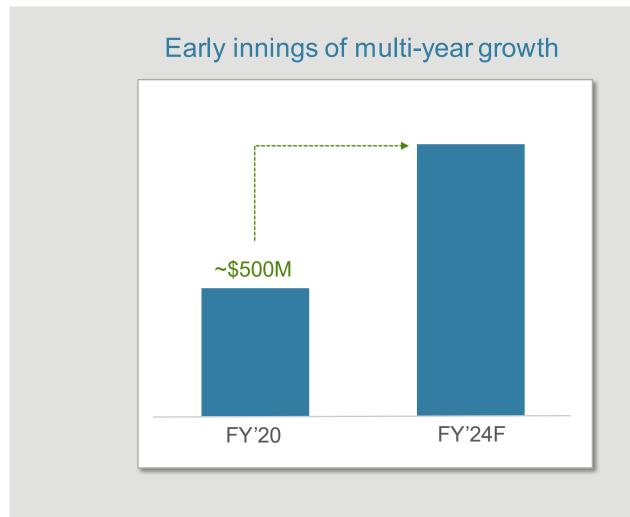

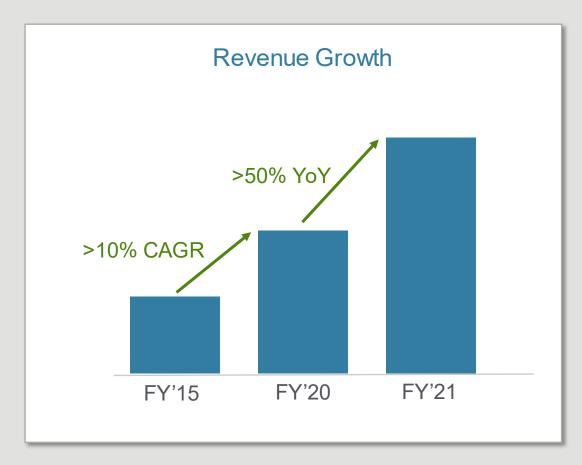

### Semi Systems Revenue Growth Drivers

<sup>\*</sup>Represents 2024 Financial Model High Scenario

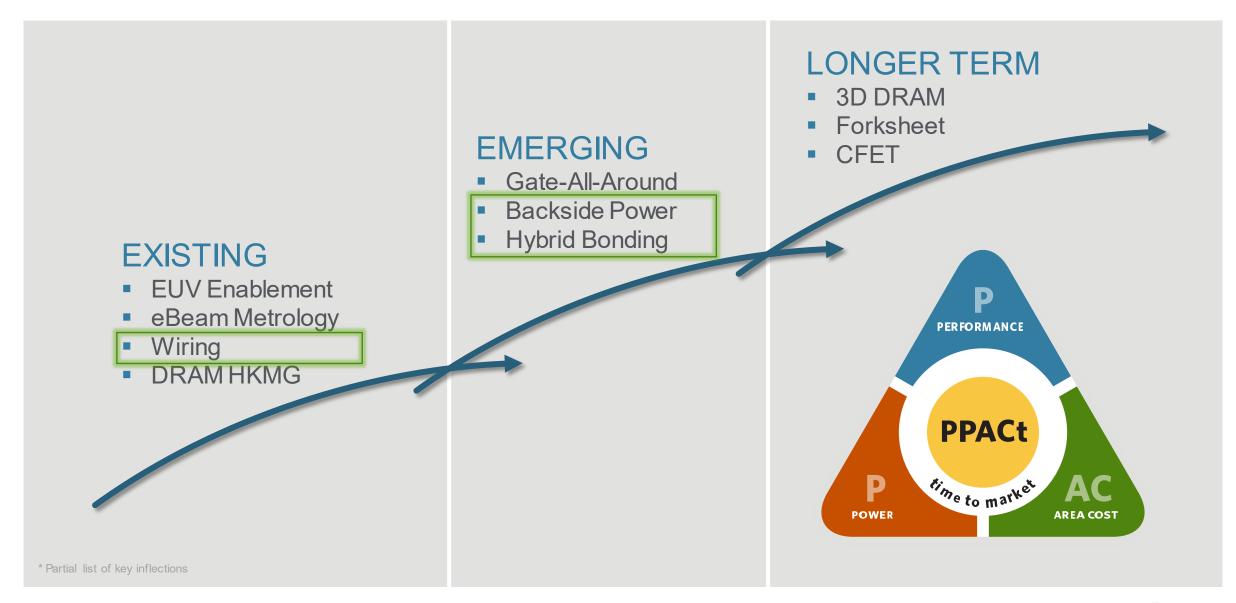

#### The New Playbook

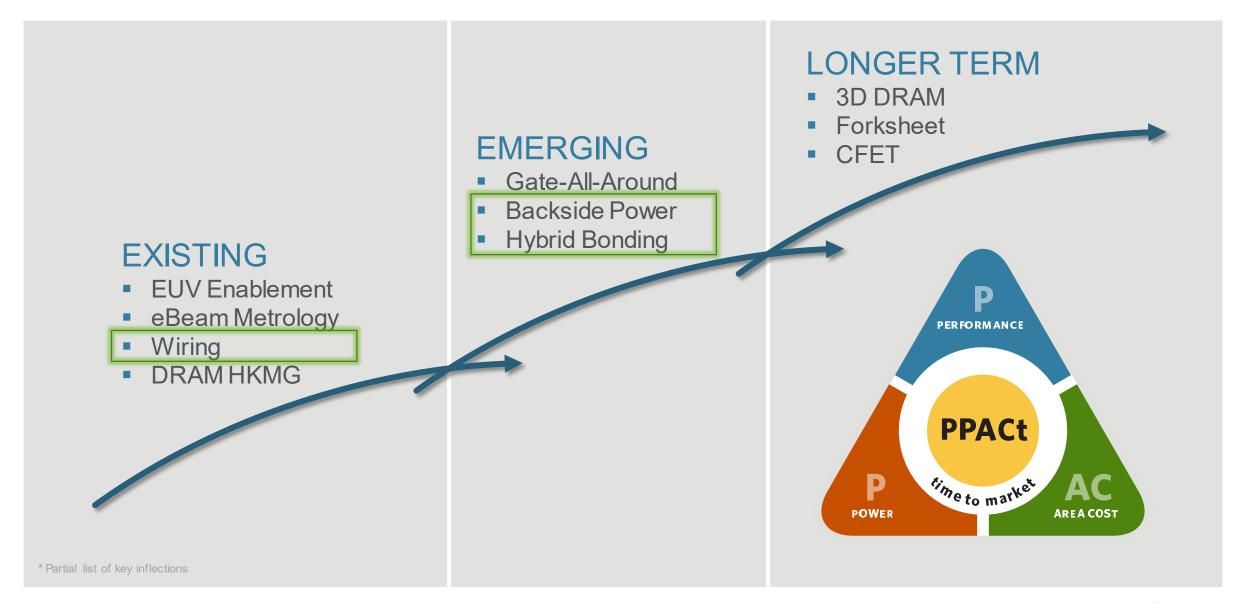

#### Inflections Over Time

#### Wiring Growth Opportunity

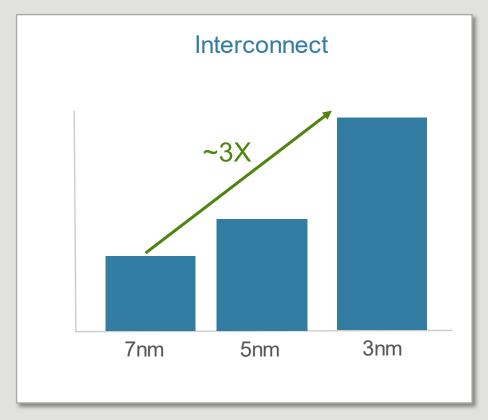

#### Expect to grow wiring revenue at ~3X the rate of WFE 2020→2024

Applied's wiring opportunity increases by >\$1B from 7nm →3nm

<sup>\*</sup>Leading Foundry/Logic Customers

#### Positioned for Growth in Packaging

- #1 in bond pad, bump and TSV

- Broad product portfolio + full-flow lab

- Key ecosystem partnerships

- Delivering system level PPACt gains: ↓ R, ↓ power, ↓ area, ↑ performance

### Packaging Growth Opportunity

### Packaging Portfolio

#### Future

- Integrated MaterialsSolution for hybrid bonding

- Large-area metrology and process control

#### Broad Portfolio Addresses all Backside Power Distribution Schemes

#### Inflections Over Time